#

### **Power-Source Selector for Dual-Battery Systems**

### **General Description**

The MAX1538 selector provides power-source control for dual-battery systems. The device selects between an AC adapter and dual batteries based on the presence of the three power sources and the state of charge of each battery. The MAX1538 includes analog comparators to detect AC/airline-adapter presence and determine battery undervoltage. Fast analog circuitry allows the device to switch between power sources to implement a break-before-make time, which allows hot swapping of battery packs. The MAX1538 independently performs power-source monitoring and selection, freeing the system power-management µP for other tasks. This simplifies the development of uP power-management firmware and allows the µP to enter standby, reducing system power consumption.

The MAX1538 supports "relearn mode," which allows the system to measure and fully utilize battery capacity. In this state, the part allows the selected battery to be discharged even when an AC adapter is present. The MAX1538 can also be used to power the system in an aircraft. On detecting an airline adapter, the MAX1538 automatically disables charging or discharging of battery packs and only allows the system to be powered from the adapter.

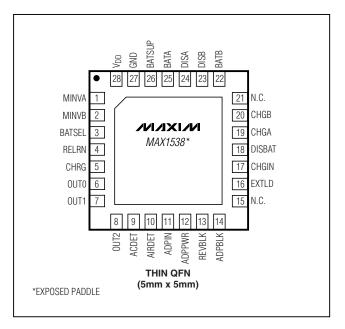

The MAX1538 is available in a space-saving 28-pin thin QFN package with a maximum footprint of 5mm x 5mm.

### **Applications**

Notebook and Subnotebook Computers Internet Tablets **Dual-Battery Portable Equipment**

Pin Configuration appears at end of data sheet.

#### **Features**

- **♦** Automatically Detects and Responds to **Low-Battery Voltage Condition Battery Insertion and Removal AC-Adapter Presence** Airline-Adapter Presence

- ♦ Step-Down and Step-Up Charger Compatibility

- ♦ Fast Break-Before-Make Selection Allows Hot Swapping of Power Sources No External Schottky Diodes Needed

- ♦ 50µA Maximum Battery Quiescent Current

- ♦ Implements Battery Capacity Relearning

- ♦ Allows Usage of Aircraft Supply

- **♦ Direct Drive of P-Channel MOSFETs**

- ♦ Simplifies Power-Management μP Firmware

- ♦ 4.75V to 28V AC-Adapter Input Voltage Range

- Small 28-Pin Thin QFN Package (5mm x 5mm)

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX1538ETI | -40°C to +85°C | 28 Thin QFN |

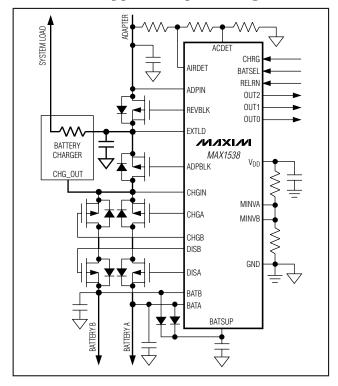

### **Typical Operating Circuit**

#### **ABSOLUTE MAXIMUM RATINGS**

| Vextld, Vbatsup, Vadpin, Vbata, Vbati                              | В,                                    |

|--------------------------------------------------------------------|---------------------------------------|

| V <sub>CHGIN</sub> to GND                                          | 0.3V to +30V                          |

| VADPPWR to GND                                                     | $-0.3V$ to $(V_{ADPIN} + 0.3V)$       |

| VREVBLK, VADPBLK to GND                                            | $-0.3V$ to $(V_{EXTLD} + 0.3V)$       |

| V <sub>CHGA</sub> , V <sub>CHGB</sub> , V <sub>DISBAT</sub> to GND | $0.3V \text{ to } (V_{CHGIN} + 0.3V)$ |

| V <sub>DISA</sub> to GND                                           | $0.3V$ to $(V_{BATA} + 0.3V)$         |

| V <sub>DISB</sub> to GND                                           | $0.3V$ to $(V_{BATB} + 0.3V)$         |

| VDD, VCHRG, VBATSEL, VRELRN, VOUTO,                                |                                       |

| VMINVA, VMINVB, VAIRDET, VACDET to                                 | GND0.3V to +6V                        |

| Continuous Power Dissipation (T <sub>A</sub> 28-Pin Thin QFN 5mm x 5mm | = +70°C)       |

|------------------------------------------------------------------------|----------------|

| (derate 20.8mW/°C above +70°                                           | °C)1666.7mW    |

| Operating Temperature Range                                            |                |

| MAX1538ETI                                                             | 40°C to +85°C  |

| Junction Temperature                                                   | +150°C         |

| Storage Temperature Range                                              | 65°C to +150°C |

| Lead Temperature (soldering, 10s                                       | s)+300°C       |

|                                                                        |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{BATA} = V_{BATB} = V_{CHGIN} = 16.8V, C_{VDD} = 1\mu\text{F}, V_{MINVA} = V_{MINVB} = 0.93V, V_{EXTLD} = V_{ADPIN} = 28V, V_{CHRG} = V_{BATSEL} = V_{RELRN} = 0, C_{ADPPWR} = C_{REVBLK} = C_{DISBAT} = C_{DISBAT} = C_{DISB} = C_{CHGA} = C_{CHGB} = 4.7n\text{F}, \textbf{T}_{\textbf{A}} = \textbf{0}^{\circ}\textbf{C} \textbf{ to +85}^{\circ}\textbf{C}, unless otherwise noted.}$  Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                                    | CON                                              | IDITIONS                                                    | MIN  | TYP  | MAX   | UNITS |

|--------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------|------|------|-------|-------|

| ADPIN, EXTLD Supply Voltage<br>Range                         |                                                  |                                                             | 4.75 |      | 28.00 | V     |

| CHGIN, BATA, BATB and<br>BATSUP Supply Voltage Range         |                                                  |                                                             | 4.75 |      | 19.00 | V     |

|                                                              |                                                  | V <sub>ADPIN</sub> = highest,<br>V <sub>ADPPWR</sub> = high |      | 21   | 50    |       |

|                                                              | V <sub>BATA</sub> = 4.75V to 19V,                | V <sub>ADPIN</sub> = highest,<br>V <sub>ADPPWR</sub> = low  |      | 23   | 54    |       |

| ADPIN, BATA, BATB, BATSUP<br>Quiescent Current (Current from | VBATB = 4.75V to 19V,<br>VBATSUP = 4.75V to 19V, | V <sub>BATA</sub> = highest,<br>V <sub>DISA</sub> = high    |      | 21   | 42    | μΑ    |

| the Highest Voltage Supply)                                  | $V_{ADPIN} = 4.75V \text{ to } 28V,$             | VBATA = highest, VDISA = low                                |      | 24   | 50    |       |

|                                                              | no external load at V <sub>DD</sub>              | V <sub>BATB</sub> = highest,<br>V <sub>DISB</sub> = high    |      | 21   | 42    |       |

|                                                              |                                                  | V <sub>BATB</sub> = highest, V <sub>DISB</sub> = low        |      | 24   | 50    |       |

|                                                              |                                                  | V <sub>BATSUP</sub> = highest                               |      | 18   | 40    |       |

| ADPIN Quiescent Current (ADPIN                               | V <sub>ADPIN</sub> = 4.75V to 18V,               | V <sub>ADPPWR</sub> = high                                  |      | 0.01 | 0.5   |       |

| Current When Not the Highest Voltage)                        | no external load at V <sub>DD</sub>              | V <sub>ADPPWR</sub> = low                                   |      | 2.6  | 6     | μΑ    |

| BATA Quiescent Current (BATA Current When Not the Highest    | $V_{BATA} = 4.75V \text{ to } 19V,$              | V <sub>DISA</sub> = high                                    |      | 3.9  | 6.0   | μA    |

| Voltage)                                                     | no external load at V <sub>DD</sub>              | V <sub>DISA</sub> = low                                     |      | 7.0  | 12    | μΑ    |

| BATB Quiescent Current (BATB Current When Not the Highest    | $V_{BATB} = 4.75V \text{ to } 19V,$              | V <sub>DISB</sub> = high                                    |      | 3.9  | 6.0   | μA    |

| Voltage)                                                     | no external load at V <sub>DD</sub>              | V <sub>DISB</sub> = low                                     |      | 7.0  | 12    | μΛ    |

| EXTLD Quiescent Current                                      | Adapter selected (REVBLI                         | K or ADPBLK pins low)                                       |      | 3.0  | 6.1   | ^     |

| LATED Quiescent Current                                      | Adapter not selected (RE\                        | /BLK and ADPBLK pins high)                                  |      | 0.02 | 1.0   | μA    |

|                                                              | AC or airline state (CHGA,                       | CHGB, and DISBAT pins high)                                 |      | 0.03 | 1.5   |       |

| CHGIN Quiescent Current                                      | Charge state (CHGA or Cl                         | HGB pin low, DISBAT pin high)                               |      | 3.1  | 6.2   | μΑ    |

| GITGITY QUICSCOTT OUT OIL                                    | Discharge or relearn state DISBAT pin low)       | (CHGA or CHGB pin low,                                      |      | 6.1  | 12.1  | μπ    |

\_\_\_ /VI/IXI/VI

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{BATA} = V_{BATB} = V_{CHGIN} = 16.8V, C_{VDD} = 1\mu\text{F}, V_{MINVA} = V_{MINVB} = 0.93V, V_{EXTLD} = V_{ADPIN} = 28V, V_{CHRG} = V_{BATSEL} = V_{RELRN} = 0, C_{ADPPWR} = C_{REVBLK} = C_{DISBAT} = C_{DISBAT} = C_{DISB} = C_{CHGB} = 4.7n\text{F}, \textbf{T}_{\textbf{A}} = \textbf{0}^{\circ}\textbf{C} \textbf{ to +85}^{\circ}\textbf{C}, unless otherwise noted.}$  Typical values are at TA = +25°C.)

| PARAMETER                                            | со                                               | NDITIONS                     | MIN   | TYP  | MAX   | UNITS   |

|------------------------------------------------------|--------------------------------------------------|------------------------------|-------|------|-------|---------|

| LINEAR REGULATOR                                     | •                                                |                              |       |      |       | •       |

| V <sub>DD</sub> Output Voltage                       | $I_{VDD} = 0$ to $100\mu A$                      |                              | 3.270 | 3.3  | 3.330 | V       |

|                                                      | VBATA or VBATB = 5V to 1                         | 19V, V <sub>ADPIN</sub> = 5V |       |      | 1.0   |         |

| V <sub>DD</sub> Power-Supply Rejection               | VBATA = VBATB = 5V, VAI                          | OPIN = 5V to 28V             |       |      | 1.0   | mV/V    |

| Ratio                                                | VBATA, VBATB, or VADPIN 10V/µs, other supplies = |                              |       | 1    |       | 11107 0 |

| V <sub>DD</sub> Undervoltage Lockout                 | Rising edge, relative to re                      | egulation point              | -55   |      | -10   | mV      |

| COMPARATORS                                          |                                                  |                              |       |      |       |         |

| ACDET, AIRDET Input Voltage<br>Range                 |                                                  |                              | 0     |      | 5.5   | V       |

| ACDET, AIRDET Input Bias<br>Current                  | VAIRDET = VACDET = 3V                            |                              |       | 0.1  | 1     | μΑ      |

| ACDET, AIRDET Trip Threshold                         | Input falling                                    |                              | 1.97  | 2.0  | 2.03  | V       |

| ACDET, AIRDET Hysteresis                             |                                                  |                              |       | 20   |       | mV      |

| MINV_ Operating Voltage Range                        |                                                  |                              | 0.93  |      | 2.60  | V       |

| MINV_ Input Bias Current                             | $V_{MINV} = 0.93V \text{ to } 2.6V$              |                              | -50   |      | +50   | nA      |

| DAT M: VIII T:                                       |                                                  | $V_{MINV} = 0.93V$           | 4.605 | 4.65 | 4.695 |         |

| BAT_ Minimum Voltage Trip Threshold                  | V <sub>BAT</sub> _ falling                       | $V_{MINV} = 1.5V$            | 7.455 | 7.5  | 7.545 | V       |

|                                                      |                                                  | $V_{MINV} = 2.6V$            | 12.93 | 13   | 13.07 |         |

| BAT_ Minimum Voltage Hysteresis                      |                                                  |                              |       | 125  |       | mV      |

| BAT_ Pack Removal Detection<br>Threshold             | V <sub>BAT</sub> falling                         |                              | 1.90  | 2.0  | 2.10  | V       |

| BAT_ Pack Removal Hysteresis                         |                                                  |                              |       | 85   |       | mV      |

| GATE DRIVERS (Note 1)                                |                                                  |                              |       |      |       |         |

| ADPPWR, REVBLK, ADPBLK,<br>DISBAT, DISA, DISB, CHGA, | VSOURCE = 15V, VPIN = 7                          | 7.5V                         | 18    | 60   |       | - mA    |

| CHGB Source Current (PMOS<br>Turn-Off)               | VSOURCE = 15V, VPIN = 1                          | 13V                          | 3     | 15   |       | IIIA    |

| ADPPWR, REVBLK, ADPBLK,<br>DISBAT, DISA, DISB, CHGA, | VSOURCE = 15V, VPIN = 1                          | 15V                          | 20    | 70   |       | 0       |

| CHGB Sink Current (PMOS<br>Turn-On)                  | V <sub>SOURCE</sub> = 15V, V <sub>PIN</sub> = 9  | ).5V                         | 10    | 55   |       | mA      |

| ADPPWR, REVBLK, ADPBLK,<br>DISBAT, DISA, DISB, CHGA, | VSOURCE = 8V to 19V (AI<br>VSOURCE = 8V to 28V)  | OPPWR, REVBLK, and AOPBLK,   | -11.0 | -9.0 | -7.0  | V       |

| CHGB Turn-On Clamp Voltage<br>(VPIN to VSOURCE)      | V <sub>SOURCE</sub> = 4.75V to 8V                |                              | -8.00 |      | -3.65 | V       |

### **ELECTRICAL CHARACTERISTICS (continued)**

(VBATA = VBATB = VCHGIN = 16.8V, CVDD= 1 $\mu$ F, VMINVA = VMINVB = 0.93V, VEXTLD = VADPIN = 28V, VCHRG = VBATSEL = VRELRN = 0, CADPPWR = CREVBLK = CADPBLK = CDISBAT = CDISBAT = CDISBAT = CCHGB = 4.7nF,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.)

| PARAMETER                                                                  | SYMBOL                    | CONDITIONS                                   | MIN | TYP | MAX  | UNITS |

|----------------------------------------------------------------------------|---------------------------|----------------------------------------------|-----|-----|------|-------|

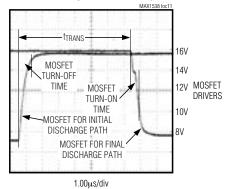

| ADPPWR, REVBLK, ADPBLK,<br>DISBAT, DISA, DISB, CHGA,<br>CHGB Turn-On Time  |                           | VSOURCE = 15V, VPIN = 13V to VPIN = 9V       |     | 0.3 | 0.88 | μs    |

| ADPPWR, REVBLK, ADPBLK,<br>DISBAT, DISA, DISB, CHGA,<br>CHGB Turn-Off Time |                           | VSOURCE = 15V, VPIN = 9V to VPIN = 13V       |     | 0.3 | 0.88 | μs    |

| STATE SELECTION INPUTS                                                     |                           |                                              |     |     |      |       |

| CHRG, BATSEL, RELRN Input<br>Low Voltage                                   |                           |                                              |     |     | 0.8  | V     |

| CHRG, BATSEL, RELRN Input<br>High Voltage                                  |                           |                                              | 2.1 |     |      | V     |

| CHRG, BATSEL, RELRN Input<br>Leakage Current                               |                           | VCHRG = VBATSEL = VRELRN = 5.5V              |     | 0.1 | 1    | μΑ    |

| STATE OUTPUTS                                                              | •                         |                                              |     |     |      |       |

| OUT0, OUT1, OUT2 Sink Current                                              |                           | V <sub>OUT</sub> _ = 0.4V                    | 1   |     |      | mA    |

| OOTO, OOTT, OOTZ SIIIK CUITEIII                                            |                           | V <sub>OUT</sub> _ = 5.5V                    | 25  |     |      | MA    |

| OUT0, OUT1, OUT2 Leakage<br>Current                                        | V <sub>OUT</sub> _ = 5.5V |                                              |     | 0.1 | 1    | μΑ    |

| TRANSITION TIMES                                                           |                           |                                              |     |     |      |       |

| MINV_ Comparator Delay                                                     | tMINV                     | $V_{BAT} = 5.5V \text{ to } V_{BAT} = 4.45V$ |     | 5.5 | 11   | μs    |

| AIRDET and ACDET Comparator Delay                                          | tadp                      | Falling edge with -20mV overdrive            |     | 2.7 | 6.0  | μs    |

| BAT_ Removal Comparator Delay                                              |                           | Falling edge with -20mV overdrive            |     | 10  |      | μs    |

| Battery-Insertion Blanking Time                                            | t <sub>BBLANK</sub>       |                                              | 13  | 21  | 31   | ms    |

| State-Machine Delay                                                        |                           |                                              |     | 50  |      | ns    |

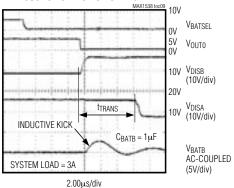

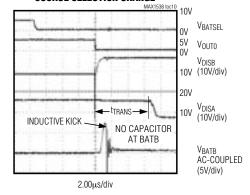

| MOSFET Turn-On Delay                                                       | ttrans                    |                                              | 5   | 7.5 | 10   | μs    |

! \_\_\_\_\_\_ /N/XI/M

#### **ELECTRICAL CHARACTERISTICS**

$(V_{BATA} = V_{BATB} = V_{CHGIN} = 16.8V, C_{VDD} = 1\mu\text{F}, V_{MINVA} = V_{MINVB} = 0.93V, V_{EXTLD} = V_{ADPIN} = 28V, V_{CHRG} = V_{BATSEL} = V_{RELRN} = 0, C_{ADPPWR} = C_{REVBLK} = C_{ADPBLK} = C_{DISBAT} = C_{DISB} = C_{CHGA} = C_{CHGB} = 4.7n\text{F}, \textbf{T}_{\textbf{A}} = \textbf{-40°C to +85°C}, unless otherwise noted.) (Note 2)$

| PARAMETER                                                   | СО                                                                     | NDITIONS                                                    | MIN   | MAX   | UNITS |

|-------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------|-------|-------|-------|

| ADPIN, EXTLD Supply Voltage<br>Range                        |                                                                        |                                                             | 4.75  | 28.00 | V     |

| CHGIN, BATA, BATB, and<br>BATSUP Supply Voltage Range       |                                                                        |                                                             | 4.75  | 19.00 | ٧     |

|                                                             |                                                                        | V <sub>ADPIN</sub> = highest,<br>V <sub>ADPPWR</sub> = high |       | 50    |       |

| ADPIN, BATA, BATB, BATSUP                                   | V <sub>BATA</sub> = 4.75V to 19V,<br>V <sub>BATB</sub> = 4.75V to 19V, | V <sub>ADPIN</sub> = highest,<br>V <sub>ADPPWR</sub> = low  |       | 54    |       |

| Quiescent Current (Current from                             | $V_{BATSUP} = 4.75V \text{ to } 19V,$                                  | V <sub>BATA</sub> = highest, V <sub>DISA</sub> = high       |       | 42    | μΑ    |

| the Highest Voltage Supply)                                 | $V_{ADPIN} = 4.75V \text{ to } 28V,$                                   | VBATA = highest, VDISA = low                                |       | 50    |       |

|                                                             | no external load at V <sub>DD</sub>                                    | V <sub>BATB</sub> = highest, V <sub>DISB</sub> = high       |       | 42    |       |

|                                                             |                                                                        | V <sub>BATB</sub> = highest, V <sub>DISB</sub> = low        |       | 50    |       |

|                                                             |                                                                        | VBATSUP = highest                                           |       | 40    |       |

| ADPIN Quiescent Current (ADPIN Current When Not the Highest | V <sub>ADPIN</sub> = 4.75V to 18V,                                     | V <sub>ADPPWR</sub> = high                                  |       | 1     | μA    |

| Voltage)                                                    | no external load at V <sub>DD</sub>                                    | V <sub>ADPPWR</sub> = low                                   |       | 9     | μ΄    |

| BATA Quiescent Current (BATA Current When Not the Highest   | V <sub>BATA</sub> = 4.75V to 19V,                                      | V <sub>DISA</sub> = high                                    |       | 7.5   | · μΑ  |

| Voltage)                                                    | no external load at V <sub>DD</sub>                                    | V <sub>DISA</sub> = low                                     |       | 16    | μΑ    |

| BATB Quiescent Current (BATB Current When Not the Highest   | V <sub>BATB</sub> = 4.75V to 19V,                                      | V <sub>DISB</sub> = high                                    |       | 7.5   | μA    |

| Voltage)                                                    | no external load at V <sub>DD</sub>                                    | V <sub>DISB</sub> = low                                     |       | 16    | μ, ,  |

| EVILD Quiescent Current                                     | Adapter selected (REVBI                                                | _K or ADPBLK pins low)                                      |       | 9.5   | ^     |

| EXTLD Quiescent Current                                     | Adapter not selected (RE                                               | VBLK and ADPBLK pins high)                                  |       | 1.0   | μΑ    |

|                                                             | AC or airline state (CHGA                                              | , CHGB, and DISBAT pins high)                               |       | 1.5   |       |

|                                                             | Charge state (CHGA or C                                                | CHGB pin low, DISBAT pin high)                              |       | 10    |       |

| CHGIN Quiescent Current                                     | Discharge or relearn state DISBAT pin low)                             | e (CHGA or CHGB pin low,                                    |       | 18.5  | μΑ    |

| LINEAR REGULATOR                                            |                                                                        |                                                             |       |       |       |

| V <sub>DD</sub> Output Voltage                              | $I_{VDD} = 0$ to $100\mu A$                                            |                                                             | 3.270 | 3.330 | V     |

| V <sub>DD</sub> Undervoltage Lockout                        | Rising edge, relative to re                                            | egulation point                                             | -60   | -10   | mV    |

| COMPARATORS                                                 |                                                                        |                                                             |       |       |       |

| ACDET, AIRDET Input Voltage<br>Range                        |                                                                        |                                                             | 0     | 5.5   | V     |

| ACDET, AIRDET Trip Threshold                                | Input falling                                                          |                                                             | 1.94  | 2.06  | V     |

| MINV_ Operating Voltage Range                               |                                                                        |                                                             | 0.93  | 2.60  | V     |

|                                                             |                                                                        | V <sub>MINV</sub> _ = 0.93V                                 | 4.59  | 4.72  |       |

| BAT_ Minimum Voltage Trip<br>Threshold                      | V <sub>BAT</sub> _ falling                                             | V <sub>MINV</sub> _ = 1.5V                                  | 7.4   | 7.6   | V     |

|                                                             |                                                                        | V <sub>MINV</sub> _ = 2.6V                                  | 12.86 | 13.14 |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

(VBATA = VBATB = VCHGIN = 16.8V, CVDD = 1 $\mu$ F, VMINVA = VMINVB = 0.93V, VEXTLD = VADPIN = 28V, VCHRG = VBATSEL = VRELRN = 0, CADPPWR = CREVBLK = CADPBLK = CDISBAT =

| PARAMETER                                                                  | SYMBOL                               | CONDITIONS                                                            | MIN     | MAX   | UNITS |

|----------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------|---------|-------|-------|

| BAT_ Pack Removal Detection<br>Threshold                                   |                                      | V <sub>BAT</sub> _ falling                                            | 1.88    | 2.12  | V     |

| GATE DRIVERS (Note 1)                                                      |                                      |                                                                       |         |       |       |

| ADPPWR, REVBLK, ADPBLK,<br>DISBAT, DISA, DISB, CHGA,                       |                                      | VSOURCE = 15V, VPIN = 7.5V                                            | 18      |       | mA    |

| CHGB Source Current (PMOS Turn-Off)                                        |                                      | VSOURCE = 15V, VPIN = 13V                                             | 3       |       | IIIA  |

| ADPPWR, REVBLK, ADPBLK, DISBAT, DISA, DISB, CHGA,                          |                                      | VSOURCE = 15V, VPIN = 15V                                             | 20      |       | mA    |

| CHGB Sink Current (PMOS<br>Turn-On)                                        |                                      | VSOURCE = 15V, VPIN = 9.5V                                            | 10      |       | IIIA  |

| ADPPWR, REVBLK, ADPBLK, DISBAT, DISA, DISB, CHGA,                          |                                      | VSOURCE = 8V to 19V (ADPPWR, REVBLK, and ADPBLK, VSOURCE = 8V to 28V) | -11.7   | -6.5  | V     |

| CHGB Turn-On Clamp Voltage (VPIN to VSOURCE)                               |                                      | VSOURCE = 4.75V to 8V                                                 | -8.00   | -3.50 | V     |

| ADPPWR, REVBLK, ADPBLK,<br>DISBAT, DISA, DISB, CHGA,<br>CHGB Turn-On Time  |                                      | VSOURCE = 15V, VPIN = 13V to VPIN = 9V                                |         | 0.88  | μs    |

| ADPPWR, REVBLK, ADPBLK,<br>DISBAT, DISA, DISB, CHGA,<br>CHGB Turn-Off Time |                                      | VSOURCE = 15V, VPIN = 9V to VPIN = 13V                                |         | 0.88  | μs    |

| STATE SELECTION INPUTS                                                     | •                                    |                                                                       |         |       | •     |

| CHRG, BATSEL, RELRN Input<br>Low Voltage                                   |                                      |                                                                       |         | 0.8   | V     |

| CHRG, BATSEL, RELRN Input<br>High Voltage                                  |                                      |                                                                       | 2.1     |       | V     |

| STATE OUTPUTS                                                              |                                      |                                                                       |         |       |       |

| OUT0, OUT1, OUT2 Sink Current                                              | $V_{OUT} = 0.4V$<br>$V_{OUT} = 5.5V$ |                                                                       | 1<br>25 |       | mA    |

| TRANSITION TIMES                                                           | <u> </u>                             |                                                                       | I       |       | l.    |

| MINV_ Comparator Delay                                                     | tMINV                                | V <sub>BAT</sub> _ = 5.5V to V <sub>BAT</sub> _ = 4.45V               |         | 11    | μs    |

| AIRDET and ACDET Comparator Delay                                          | tadp                                 | Falling edge with -20mV overdrive                                     |         | 6     | μs    |

| Battery-Insertion Blanking Time                                            | t <sub>BBLANK</sub>                  |                                                                       | 12      | 31    | ms    |

| MOSFET Turn-On Delay                                                       | ttrans                               |                                                                       | 5       | 10    | μs    |

**Note 1:** V<sub>PIN</sub> refers to the voltage of the driver output. V<sub>SOURCE</sub> refers to the power source for the driver. ADPPWR, REVBLK, ADPBLK, DISBAT, DISA, DISB, CHGA, and CHGB gate drivers correspond to sources at ADPIN, EXTLD, EXTLD, CHGIN, BATA, BATB, CHGIN, and CHGIN, respectively.

Note 2: Guaranteed by design. Not production tested.

6 \_\_\_\_\_\_\_*NIXI/*U

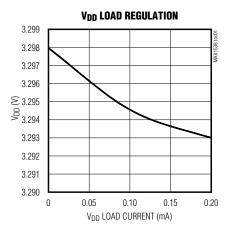

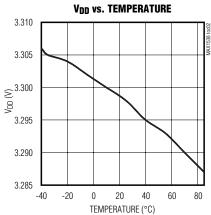

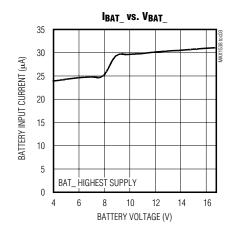

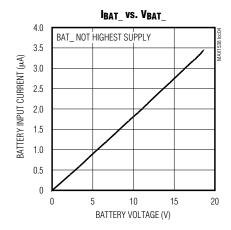

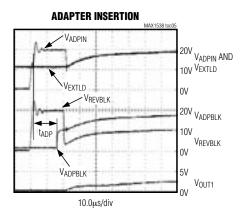

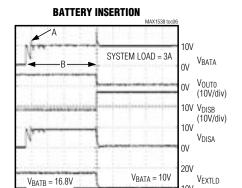

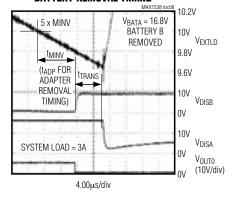

### Typical Operating Characteristics

(Circuit of Figure 1.  $T_A = +25$ °C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(Circuit of Figure 1.  $T_A = +25$ °C, unless otherwise noted.)

10V

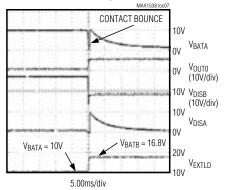

5.00ms/div A: CONTACT BOUNCE B: BATTERY INSERTION BLANKING TIME = 22ms

#### **BATTERY REMOVAL TIMING**

#### **BATTERY REMOVAL**

#### **SOURCE SELECTION CHANGE**

#### **SOURCE SELECTION CHANGE**

### Typical Operating Characteristics (continued)

FIRST SOURCE INSERTION

200µs/div

POWER-UP TIME

(Circuit of Figure 1.  $T_A = +25$ °C, unless otherwise noted.)

#### BREAK-BEFORE-MAKE TIMING

# MAX1538 Ide12 5V OUT1 0V OUT2, OUT0 20V VADPIN 10V VREVBLK

0V

20V 10V V<sub>EXTLD</sub>

0V

### Pin Description

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                            |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | MINVA  | Minimum Battery A Voltage Set Point. Battery A discharge is prevented if V <sub>BATA</sub> has fallen below 5 x V <sub>MINVA</sub> .                                                                                                                                                                                |

| 2   | MINVB  | Minimum Battery B Voltage Set Point. Battery B discharge is prevented if V <sub>BATB</sub> has fallen below 5 x V <sub>MINVB</sub> .                                                                                                                                                                                |

| 3   | BATSEL | Battery-Selection Input. Drive to logic low to charge battery A or give discharge preference to battery A. Drive to logic high to charge battery B or give discharge preference to battery B.                                                                                                                       |

| 4   | RELRN  | Battery-Relearn Logic-Level Input. Drive RELRN high to enable battery-relearn mode.                                                                                                                                                                                                                                 |

| 5   | CHRG   | Charge-Enable Logic-Level Input. Drive CHRG high to enable the charging path from the charger to the battery selected by BATSEL.                                                                                                                                                                                    |

| 6   | OUT0   |                                                                                                                                                                                                                                                                                                                     |

| 7   | OUT1   | Selector-State Output. This open-drain output indicates the state of the MAX1538. See Table 1 for information on decoding.                                                                                                                                                                                          |

| 8   | OUT2   | information on decoding.                                                                                                                                                                                                                                                                                            |

| 9   | ACDET  | AC-Adapter Detection Input. When V <sub>ACDET</sub> is greater than the ACDET trip threshold (2V typ), adapter presence is detected.                                                                                                                                                                                |

| 10  | AIRDET | Airline-Adapter Detection Input. When V <sub>AIRDET</sub> > 2V and V <sub>ACDET</sub> < 2V, the airline-adapter presence is detected. Charging is disabled when an airline adapter is detected.                                                                                                                     |

| 11  | ADPIN  | Adapter Input. When V <sub>ADPIN</sub> > V <sub>BATSUP</sub> , the MAX1538 is powered by ADPIN. ADPIN is the supply rail for the ADPPWR MOSFET driver.                                                                                                                                                              |

| 12  | ADPPWR | Adapter-Power P-Channel MOSFET Driver. Connect ADPPWR to the gate of P1 (Figure 1). P1 disconnects the adapter from the system during relearn mode. Exclude P1 and leave ADPPWR disconnected if relearn is not used. ADPPWR is driven relative to ADPIN. ADPPWR and REVBLK are driven with the same control signal. |

| 13  | REVBLK | Gate Drive for the Reverse-Blocking P-Channel MOSFET. Connect REVBLK to the gate of P2 (Figure 1). P2 enables and disables the AC adapter's power path. REVBLK is driven relative to EXTLD. REVBLK and ADPPWR are driven with the same control signal.                                                              |

### Pin Description (continued)

|        | T               |                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN    | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                        |

| 14     | ADPBLK          | Gate Drive for the Adapter-Blocking P-Channel MOSFET. Connect ADPBLK to the gate of P3 (Figure 1). P3 enables and disables the battery discharge path. ADPBLK is driven relative to EXTLD. ADPBLK and DISBAT are driven with the same control signal.                                                                                                           |

| 15, 21 | N.C.            | Not Internally Connected                                                                                                                                                                                                                                                                                                                                        |

| 16     | EXTLD           | External Load. EXTLD is the supply rail for REVBLK and ADPBLK.                                                                                                                                                                                                                                                                                                  |

| 17     | CHGIN           | Charger Node Input. CHGIN is the supply rail for DISBAT, CHGA, and CHGB.                                                                                                                                                                                                                                                                                        |

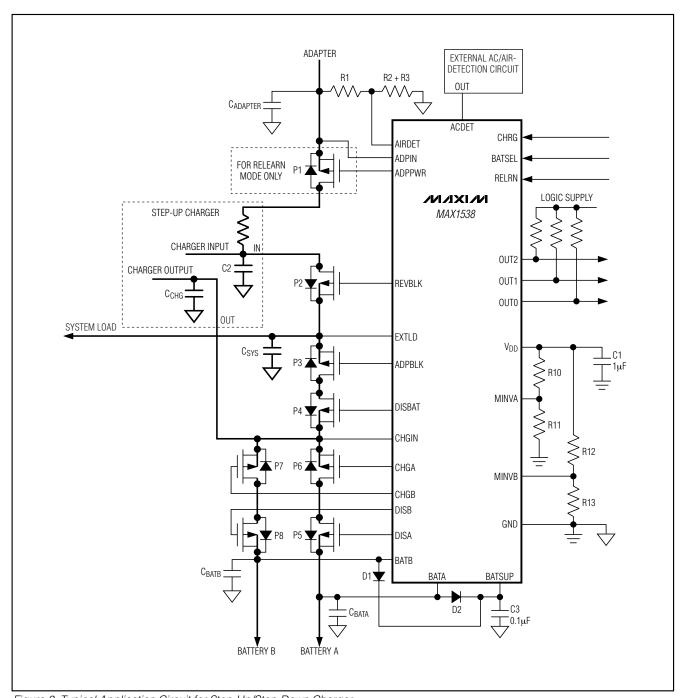

| 18     | DISBAT          | Gate Drive for the Battery-Discharge P-Channel MOSFET. Connect DISBAT to the gate of P4 (Figure 2). P4 disconnects the battery from the system load when charging from a step-up converter. Exclude P4 and leave DISBAT disconnected if using a step-down charger. DISBAT is driven relative to CHGIN. DISBAT and ADPBLK are driven by the same control signal. |

| 19     | CHGA            | Gate Drive for the Charge Battery A P-Channel MOSFET. Connect CHGA to the gate of P6 (Figure 1). P6 enables and disables the charge path into battery A. CHGA is driven relative to CHGIN. CHGA and DISA are driven by the same control signal.                                                                                                                 |

| 20     | CHGB            | Gate Drive for the Charge Battery B P-Channel MOSFET. Connect CHGB to the gate of P7 (Figure 1). P7 enables and disables the charge path into battery B. CHGB is driven relative to CHGIN. CHGB and DISB are driven by the same control signal.                                                                                                                 |

| 22     | BATB            | Battery B Voltage Input. Battery undervoltage and absence is determined by measuring BATB. BATB is the supply rail for DISB.                                                                                                                                                                                                                                    |

| 23     | DISB            | Gate Drive for the Discharge from Battery B P-Channel MOSFET. Connect DISB to the gate of P8 (Figure 1). P8 enables and disables the discharge path from battery B. DISB is driven relative to BATB. DISB and CHGB are driven by the same control signal.                                                                                                       |

| 24     | DISA            | Gate Drive for the Discharge from Battery A P-Channel MOSFET. Connect DISA to the gate of P5 (Figure 1). P5 enables and disables the discharge path from battery A. DISA is driven relative to BATA. DISA and CHGA are driven by the same control signal.                                                                                                       |

| 25     | BATA            | Battery A Voltage Input. Battery undervoltage and absence is determined by measuring BATA. BATA is the supply rail for DISA.                                                                                                                                                                                                                                    |

| 26     | BATSUP          | BATSUP powers the MAX1538. Diode OR BATA and BATB to BATSUP externally. ADPIN is diode connected to BATSUP internally. Bypass with a 0.1µF capacitor from BATSUP to GND.                                                                                                                                                                                        |

| 27     | GND             | Ground                                                                                                                                                                                                                                                                                                                                                          |

| 28     | V <sub>DD</sub> | Linear-Regulator Output. Bypass with a 1µF capacitor from V <sub>DD</sub> to GND.                                                                                                                                                                                                                                                                               |

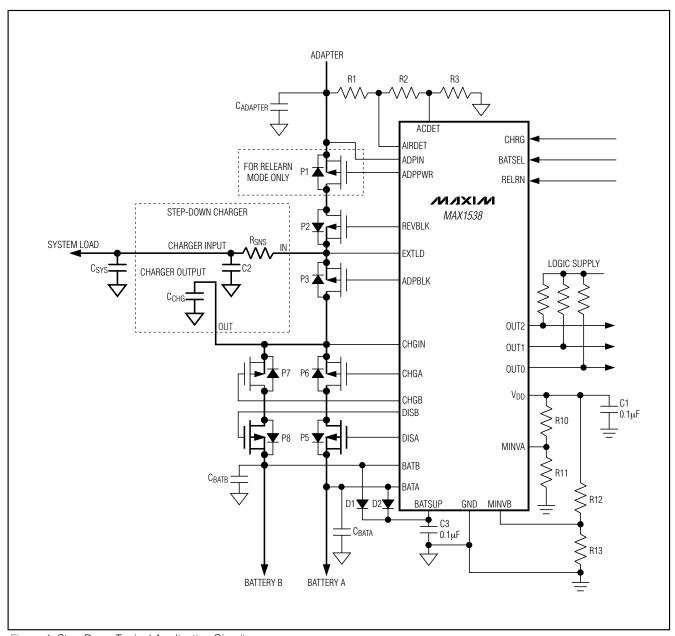

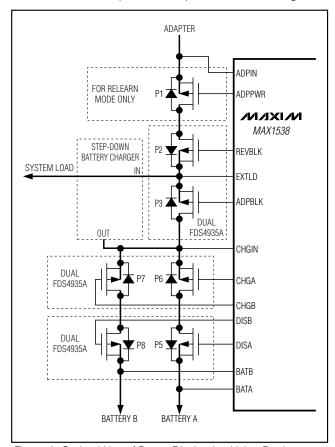

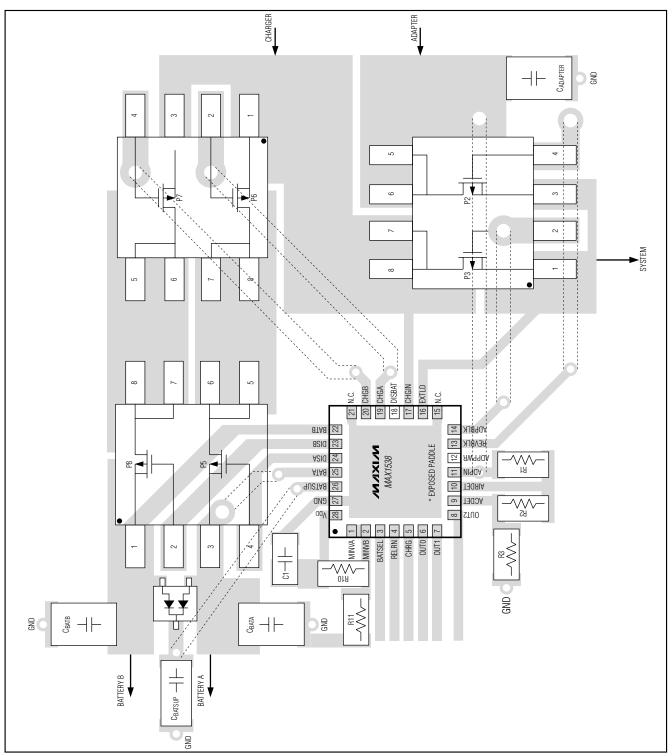

Figure 1. Step-Down Typical Application Circuit

Figure 2. Typical Application Circuit for Step-Up/Step-Down Charger

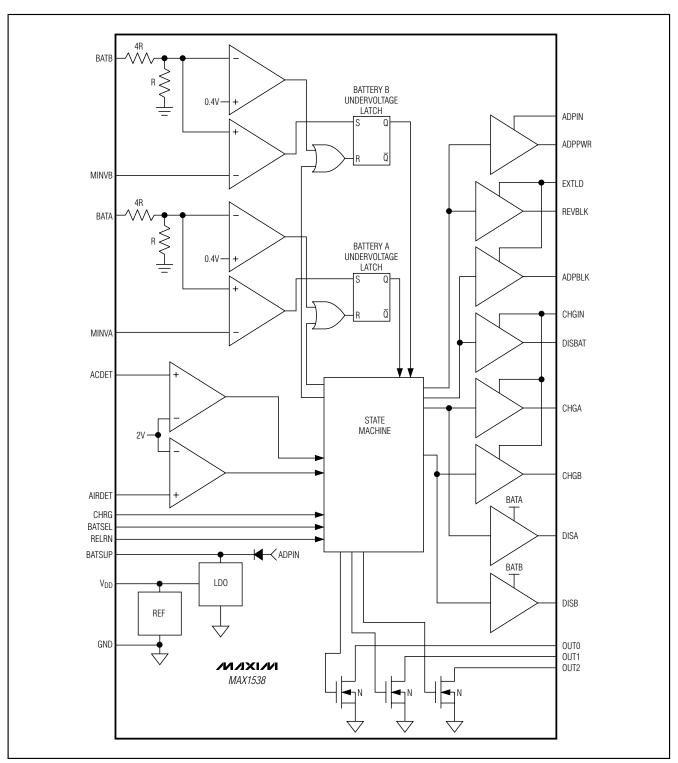

Figure 3. Functional Diagram

### Detailed Description

The MAX1538 performs power path selection between an adapter input and two batteries, relieving the host system from the burden of real-time response to power-source changes. The integrated selector implements a fixed break-before-make timer to ensure that power sources are not connected together and yet the load is not left unserviced. The MAX1538 monitors battery and adapter state and presence to determine which source to select and whether to charge the battery. Logic inputs CHRG, BATSEL, and RELRN allow the host to enable/disable charging, select which battery to use, and impose battery discharge even with adapter presence. The MAX1538 automatically detects airline adapters and prevents charging when an airline adapter is detected. Open-drain logic outputs OUT2,

OUT1, and OUT0 indicate the state of the selector so the host can properly respond.

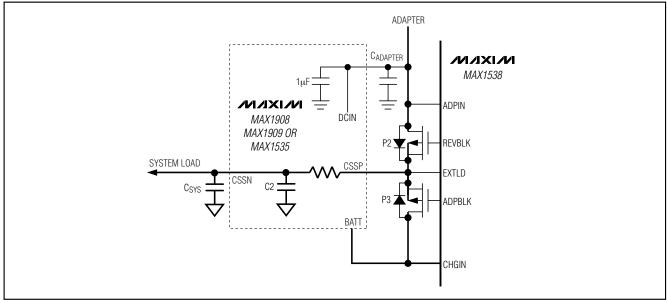

The MAX1538 can be configured for use with a step-down battery charger, as shown in Figure 1, or with a step-up/step-down battery charger, as shown in Figure 2. The minimum MAX1538 system requires only six MOSFETs. The MAX1538 provides relearn-mode support with the addition of P1. Relearn mode allows the system to relearn the battery's capacity without user intervention.

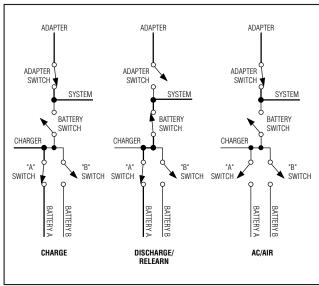

Table 1 summarizes the possible states and configurations of the MAX1538.

Table 1. MAX1538 State Table

| SOURC   | E ST    | ATE        | LOG     | SIC IN  | PUTS                  | М                                                 | OSFET STATE                       | (See Figure 4)               | l                            |       |       |        |                |

|---------|---------|------------|---------|---------|-----------------------|---------------------------------------------------|-----------------------------------|------------------------------|------------------------------|-------|-------|--------|----------------|

| Adapter | Ba<br>A | ttery<br>B | CHG     | RELRN   | BATSEL                | System<br>(ADPPWR<br>and REVBLK)                  | Battery<br>(ADPBLK<br>and DISBAT) | BATT A<br>(CHGA and<br>DISA) | BATT B<br>(CHGB and<br>DISB) | OUT2  | OUT1  | OUT0   | STATE          |

| AC      | Х       | Х          | 1       | 0       | 0                     | On                                                | Off                               | On                           | Off                          | 1     | 1     | 0      | Charge A       |

| AC      | Χ       | Χ          | 1       | 0       | 1                     | On                                                | Off                               | Off                          | On                           | 1     | 1     | 1      | Charge B       |

| AC      | N       | Χ          | Χ       | 1       | 0                     | Off                                               | On                                | On                           | Off                          | 1     | 0     | 0      | Relearn A      |

| AC      | Χ       | N          | Χ       | 1       | 1                     | Off                                               | On                                | Off                          | On                           | 1     | 0     | 1      | Relearn B      |

| AC      |         | 0          | therwi  | se      |                       | On                                                | Off                               | Off                          | Off                          | 0     | 1     | 0      | AC adapter     |

|         |         |            |         |         |                       |                                                   |                                   |                              |                              |       |       |        |                |

| AIR     | Χ       | Χ          | Χ       | Χ       | Χ                     | On                                                | Off                               | Off                          | Off                          | 0     | 1     | 1      | Airline        |

| Absent  | N       | Χ          | Χ       | Χ       | 0                     | Off                                               | On                                | On                           | Off                          | 0     | 0     | 0      | Discharge A    |

| Absent  | N       | U          | Χ       | Χ       | Χ                     | Oli                                               | On                                | On                           | Oli                          | U     | U     | Ü      | Discharge A    |

| Absent  | Χ       | N          | Χ       | Χ       | 1                     | Off                                               | On                                | Off                          | On                           | 0     | 0     | 1      | Discharge B    |

| Absent  | U       | N          | Χ       | Χ       | Χ                     | Oli                                               | On                                | Oli                          | OII                          | U     | U     |        | Discharge D    |

| Absent  | U       | U          | Χ       | Χ       | Χ                     | Off                                               | Off                               | Off                          | Off                          | 0     | 0     | 0      | Idle           |

| Legend  |         |            |         |         |                       |                                                   |                                   |                              |                              |       |       |        |                |

| AC      | AC a    | dapter     | is pre  | sent. ' | VACDET                | and VAIRDET are                                   | e both above 2V                   |                              |                              |       |       |        |                |

| AIR     | Airlin  | ie adap    | ter is  | prese   | nt. V <sub>AC</sub>   | DET is below 2V a                                 | and V <sub>AIRDET</sub> is a      | bove 2V.                     |                              |       |       |        |                |

| Absent  | Exte    | rnal ada   | apter i | s abse  | ent. V <sub>A</sub> ( | DDET and VAIRDE                                   | Tare both below                   | v 2V.                        |                              |       |       |        |                |

|         | N       |            |         |         |                       | attery is normal. T<br><i>Battery Presence</i>    |                                   |                              |                              | the u | ınde  | rvolta | age latch (5 x |

|         | U       |            |         |         |                       | attery has tripped<br>below 5 x V <sub>MINV</sub> |                                   | •                            |                              | _     |       | •      |                |

|         |         | Ot         | herwi   | ise     |                       | Otherwise cove                                    | rs all cases not e                | explicitly show              | n elsewhere in               | the   | table | 9.     |                |

|         | Х       | Χ          | Χ       | Χ       | Χ                     | X indicates don                                   |                                   |                              |                              |       |       |        | IX.            |

Figure 4. MAX1538 Selection States

#### Battery Presence and Undervoltage Detection

The MAX1538 determines battery absence and undervoltage and does not allow discharge from an undervoltage battery. A battery is considered undervoltage when  $V_{BAT} < 5 \times V_{MINV}$ , and remains classified as undervoltage until  $V_{BAT}$  falls below 2V and again rises above  $5 \times V_{MINV}$ . The undervoltage latch is also cleared when the charge path is enabled. Set the battery undervoltage threshold using resistive voltage-dividers R10, R11, R12, and R13, as shown in Figure 1. The corresponding undervoltage threshold is:

$$V_{BATA\_Undervoltage} = 5 \times V_{DD} \times \frac{R11}{R10 + R11}$$

$$V_{BATB\_Undervoltage} = 5 \times V_{DD} \times \frac{R13}{R12 + R13}$$

To minimize error, use 1% or better accuracy divider resistors, and ensure that the impedance of the divider results in a current about 100 times the MINV\_ input bias current at the MINV\_ threshold voltage. To optimize error due to 50nA input bias current at MINV\_ and minimize current consumption, typically choose resistors (R10 + R11) or (R12 + R13) smaller than  $600k\Omega$ .

Since batteries often exhibit large changes in their terminal voltage when a load current is removed, further discharge after the undervoltage latch has been set is not allowed until the battery is removed or the charge path to the battery is selected. Battery removal is detected when VBAT\_ falls below 2V. For correct detection of battery removal, ensure that the leakage current into BAT\_ is lower than the leakage current out of BAT\_ so that BAT\_ falls below 2V when the battery is removed. The contributors to leakage current into BAT\_ are D1, D2, P6, and P7.

#### **Battery Relearn Mode**

The MAX1538 implements a battery relearn mode, which allows for host-device manufacturers to implement a mode for coulomb-counting fuel gauges (such as the MAX1781) to measure battery capacity without user intervention. In battery relearn mode, the AC adapter is switched off and battery discharge is selected. In this implementation, the host system could prompt users when their battery capacity becomes inaccurate, use the host system as a load to discharge the battery, and then recharge the battery fully. Coulomb-counting fuel-gauge accuracy is increased after a relearning cycle.

Battery relearn mode requires the addition of MOSFET P1, which blocks current from the adapter to the system. To enable relearn mode, drive RELRN high and drive BATSEL low to relearn battery A or high to relearn battery B. Relearn mode overrides the functionality of the CHG pin. Battery relearn mode does not occur when the selected battery's undervoltage latch has been set, or when the selector is in airline mode (see the *Airline Mode and AC Adapter* section.) The RELRN pin only applies when an AC adapter is present. If the AC adapter is absent and RELRN is ignored, OUT[2:1] = 10 when the MAX1538 is in battery relearn mode. If CHG = 0, only OUT2 is needed to indicate that the MAX1538 was properly placed in relearn mode.

If the selected battery trips the undervoltage latch when in relearn mode, the AC adapter is switched in without causing a crash to the system. OUT2 can indicate that the relearn cycle is terminated due to battery undervoltage. Typically, after the host system performs a battery relearn cycle, it either charges the discharged battery or begins a relearn cycle on the other battery. To switch to charge mode, drive RELRN low and CHG high. Since RELRN overrides CHG, in many applications it is best to permanently keep CHG high and reduce the IO needed to control the selector.

When the AC adapter is available, it is used as the power source for EXTLD unless the RELRN pin is high. In this state, the charger can be enabled and a battery charged.

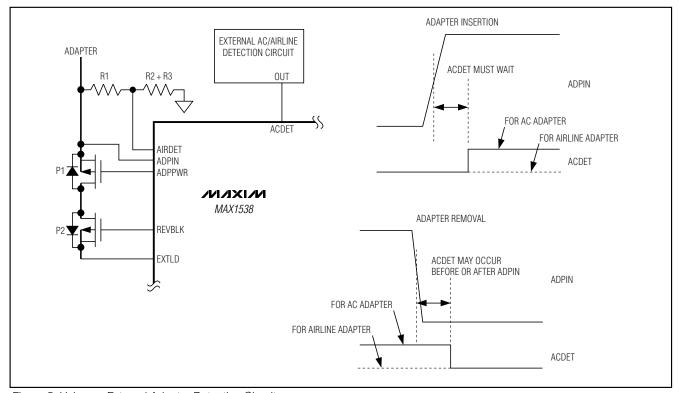

#### Airline Mode and AC Adapter

The MAX1538 provides compatibility with airline adapters. For airplane safety, the use of an airline adapter requires that the battery charger or charge path is disabled. The MAX1538 disables the charge path when an airline adapter is detected. In airline mode, ADPPWR and REVBLK drive P1 and P2 on, and all other MOSFETs are off, regardless of the state of RELRN, CHG, BATSEL, or the batteries. If the AC threshold is above the airline threshold, select a resistive voltage-divider (as shown in Figure 1) according to the following equations:

$$V_{AC\_Threshold} = V_{ACDET\_Threshold} \times \frac{R1 + R2 + R3}{R3}$$

$$V_{Air\_Threshold} = V_{AIRDET\_Threshold} \times \frac{R1 + R2 + R3}{R2 + R3}$$

where VACDET\_Threshold and VAIRDET\_Threshold are typically 2.0V (see the *Electrical Characteristics*). An AC adapter is detected when the adapter voltage is above VAC\_Threshold, and an airline adapter is detected when

the adapter voltage is between  $V_{AC\_Threshold}$  and  $V_{AlR\_Threshold}$ .

To minimize error, use 1% accuracy or better divider resistors, and ensure that the impedance of the divider results in a current about 100 times the ACDET and AIRDET input bias current. To optimize error due to 1 $\mu$ A input bias current at ACDET/AIRDET and minimize current consumption, typically choose R3 less than  $20k\Omega$ . See the Adapter Removal Debouncing section for more information regarding R1, R2, and R3. Short R2 to disable airline-adapter mode.

Optionally, an external circuit can be implemented to determine the presence of an AC/airline adapter. The circuit in Figure 5 provides fast detection of an airline adapter, yet allows external circuitry to discriminate between airline and AC adapters. If VAC\_Threshold < VAIR\_Threshold, this circuit must be used for airline-adapter detection. Other permutations that directly drive AIRDET instead do not work properly on the MAX1538 because adapter removal is not detected fast enough, causing the system load to crash.

OUT[2:0] = 011 if the MAX1538 is in airline-adapter mode. If RELRN = 0 and CHG = 0, only OUT[1:0] are necessary to indicate airline-adapter mode.

Figure 5. Using an External Adapter Detection Circuit

#### **CHG Control**

Toggle CHG to enable the charge path to the battery. Charge control is overridden by RELRN (see the *Battery Relearn Mode* section) or airline mode (see the *Airline Mode and AC Adapter* section). When CHG is enabled, the MAX1538 connects the selected battery (BATSEL = 0 for battery A and BATSEL = 1 for battery B) to the charger. OUT[2:1] = 11 if the MAX1538 is in charge mode. When the charge path is enabled, the corresponding battery undervoltage latch is cleared. This allows charging of protected battery packs. In typical applications, connect CHRG to VDD to reduce the system I/O.

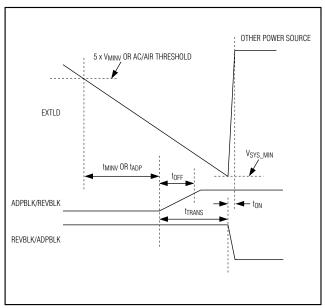

#### Single Transition Break-Before-Make Selection

The MAX1538 guarantees that no supplies are connected to each other during any transition by implementing a fixed delay time (ttrans, the break-before-make transition timer). This is necessary as the batteries have very low impedances, and momentarily shorting batteries together can cause hundreds of amps to flow. For example, when adapter removal is detected, ADPPWR and REVBLK begin to turn off less than 10µs before ADPBLK and DISBAT begin to turn on, connecting the appropriate battery. For example, upon switching from one battery to another, DISA and CHGA begin turning off less than 10µs before DISB and CHGB begin to turn on. To guarantee a break-before-make time, ensure that the turn-off time of the MOSFETs is smaller than ttrans (see the MOSFET Selection section).

The MAX1538 also guarantees that any change does not cause unnecessary power-source transitions. When switching from battery to battery; battery to adapter; or adapter to battery because of adapter or battery insertion or removal, or due to a change at BATSEL, a single set of MOSFETs are turned off followed by another set of MOSFETs turned on. No additional transitions are necessary. The only exception occurs when RELRN is high and the adapter is inserted because it is first detected as an airline adapter and later detected as an AC adapter. This results in a transition from discharge mode to AC mode, followed by a transition from AC mode to relearn mode. Although this extra transition is generally harmless, it can be avoided by disabling relearn mode when the adapter is absent.

#### Blanking

The MAX1538 implements sophisticated blanking at the adapter and the batteries to correctly determine battery/adapter insertion and removal. Logic inputs CHRG, RELRN, and BATSEL should be debounced to ensure that fast repetitive transitions do not occur, in which

case the system holdup capacitor is not large enough to sustain the system load.

Battery insertion is automatically debounced using the battery-insertion blanking time (tBBLANK). A battery is not discharged unless the battery has been above the 5 x V<sub>MINV</sub> threshold for 21ms (typ). After t<sub>BBLANK</sub> is expired, V<sub>BAT</sub> must exceed 5 x V<sub>MINV</sub> or the battery is detected as undervoltage.

### Applications Information

#### **MOSFET Selection**

Select P-channel MOSFETs P1–P8 according to their power dissipation, RDSON, and gate charge. Each MOSFET must be rated for the full system load current. Additionally, the battery discharge MOSFETs (P3, P5, P6, P7, and P8) should be selected with low on-resistance for high discharge efficiency. Since for any given switch configuration at least half of the MOSFETs are off, dual MOSFETs can be used without reducing the effective MOSFET power dissipation. When using dual

Figure 6. Optimal Use of Power Dissipation Using Dual MOSFETs

MOSFETs, they should be paired as shown in Figure 6 for optimal power dissipation.

The MAX1538 provides asymmetric MOSFET gate drive, typically turning MOSFETs on faster than they are turned off. The ttrans timer ensures that the MOSFETs that are turning on begin to turn on 10µs after those MOSFETs that are turning off begin to turn off. Choose MOSFETs with low enough gate charge that all off-transitioning MOSFETs turn off before any on-transitioning MOSFET turns on. Use the following equations to estimate the worst-case turn-on and turn-off times:

$$t_{ON} = \frac{Q_G}{V_G} \left( \frac{\Delta V_1}{I_{OFF1}} + \frac{\Delta V_2}{I_{OFF2}} \right) = \frac{Q_G}{V_G} \times 0.93 \text{k}\Omega$$

$$t_{ON} = \frac{Q_G}{V_G} \times \frac{5V}{I_{ON}} = \frac{Q_G}{V_G} \times 0.25 k\Omega$$

where ton is the turn-on time, toff is the turn-off time, QG is the MOSFET's total gate charge specified at voltage VG, IoFF1 is the 18mA (min) gate current when driving the gate from 7.5V gate drive to 2V gate drive,  $\Delta V_1$  is the voltage change during the 18mA gate drive (5.5V), IoFF2 is 3mA gate current when driving the gate from 2V to 0V,  $\Delta V_2$  is the 2V change, and IoN is the turn-on current.

The MAX1538's gate-drive current is nonlinear and is a function of gate voltage. For example, the gate driver

slows down as the MOSFET approaches off. See the *Typical Operating Characteristics* for a scope shot showing MAX1538 turn-on and turn-off times when driving FDS6679 MOSFETs. The MAX1538 typically turns the FDS6679 on in 0.7µs and off in 1µs.

#### Combining the MAX1538 with a Charger

To configure the MAX1538 for use with a step-down charger, use the circuit of Figure 7. Connect the charger's power input to EXTLD. Do not connect the charger's power input to ADPIN. This ensures that the charger does not bias ADPIN through its high-side MOSFET.

#### **System Holdup Capacitor**

Csys must be capable of sustaining the maximum system load during the transition time between source selection. Size the capacitor so that:

$$\frac{5 \times V_{MINV} - (t_{MINV} + t_{TRANS} + t_{ON}) \times}{\frac{I_{SYS} - MAX}{C_{SYS}}} > V_{SYS} - MIN$$

where t<sub>MINV</sub> is the battery undervoltage comparator delay, t<sub>TRANS</sub> is the fixed time between switching MOSFETs off and switching MOSFETs on, t<sub>ON</sub> is the time to turn a MOSFET on (see the *MOSFET Selection* section), V<sub>MINV</sub> is the lower of V<sub>MINVA</sub> and V<sub>MINVB</sub>, I<sub>SYS\_MAX</sub> is the maximum system load, V<sub>SYS\_MIN</sub> is the minimum allowable system voltage before system

Figure 7. Combining the MAX1538 with a Charger

Figure 8. System Holdup Capacitor Timing

crash, and CSYS is the total system holdup capacitance, which does not need to be near the MAX1538. The timing related to the system holdup capacitance is shown in Figure 8.

Charger output capacitance contributes to CSYS for the step-down charger topology (Figure 1), but not for the step-up/step-down charger topology (Figure 2).

#### Leakage Current into BAT\_

Leakage current into BATA or BATB can interfere with proper battery-removal detection. D1 and D2 must be low leakage to ensure that battery removal is properly detected. Choose MOSFETs P6 and P7 with low off-leakage current. Board leakage current can also be a problem. For example, neighbor pins BATA and BATSUP should have greater than  $50\text{M}\Omega$  impedance between each other. Proper battery-removal detection requires that:

where I<sub>Board</sub> is board leakage current, I<sub>DS\_OFF</sub> is the off-leakage current of MOSFETs P6 and P7, I<sub>D\_Leakage</sub> is the reverse leakage current of the diodes, and I<sub>BAT\_Sink@2V</sub> is the BAT\_ leakage current at 2V (0.4μA; see the *Typical Operating Characteristics*).

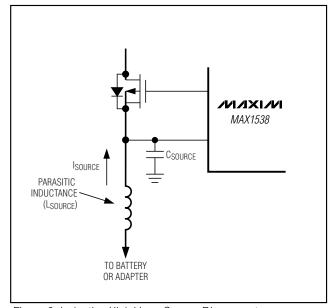

Figure 9. Inductive Kick Upon Source Disconnect

#### Inductive "Kick"

When the adapter or a battery is delivering a significant current to the system and that path is disabled (typically to enable another path), a voltage spike is generated at the source. This is due to a parasitic inductance shown in Figure 9. When the adapter is disconnected, a positive voltage spike occurs at ADPIN. When a discharging battery is disconnected, a positive voltage spike occurs at BAT\_. Connect a capacitor from BAT\_ or ADPIN to GND to limit this inductive kick. Choose the source capacitance according to the following equation:

$$C_{SOURCE} > \frac{L_{SOURCE} \times l_{SYS\_MAX}^{2}}{30^{2} - V_{SOURCE}^{2}}$$

where V<sub>SOURCE</sub> is the maximum DC voltage of the source in question, I<sub>SYS\_MAX</sub> is the maximum system load, and L<sub>SOURCE</sub> (parasitic inductance) and C<sub>SOURCE</sub> are shown in Figure 9.

During battery charge, the voltage spike during battery disconnect is negative. To ensure that this negative voltage spike does not go below 0V, choose C<sub>BAT</sub> according to the following equation:

$$C_{BAT_{-}} > \frac{L_{BAT_{-}} \times I_{CHG_{-}MAX}}{V_{BAT_{-}MIN}}^{2}$$

where VBAT\_MIN is the minimum battery voltage, ICHG\_MAX is the maximum charge current, and LBAT\_ is the battery's inductance. CBAT\_ values of 0.01µF are adequate for typical applications. Adding capacitance at BAT\_ pins lengthens the time needed to detect battery removal. See the *Battery-Absence-Detection Delay* section.

#### **Adapter Removal Debouncing**

Upon adapter removal the adapter's connector may bounce. To avoid false detection of adapter reinsertion select R1, R2, and R3 according to the following equation:

R1 + R2 + R3

$$< \frac{V_{Threshold} \times t_{Bounce}}{C_{ADPIN} \times (V_{Adapter} - V_{Threshold})}$$

where V<sub>Adapter</sub> is the AC-adapter voltage when removing an AC adapter and airline-adapter voltage when removing an airline adapter, C<sub>ADPIN</sub> is the capacitance at ADPIN, and t<sub>Bounce</sub> is the 5ms debounce time. See the *Airline Mode and AC Adapter* section for a definition of V<sub>Threshold</sub>.

#### **Battery-Absence-Detection Delay**

When a selected battery is removed, the system load quickly pulls BAT\_ below 5 x VMINV\_ and another source is selected. The battery is considered present and undervoltage until VBAT\_ falls below 2V. Although another power source is quickly switched to the system load, capacitance at BAT\_ (see the *Inductive "Kick"* section) delays the detection of the removed battery. If another battery is inserted before this delay has passed, it is considered undervoltage. Calculate the delay using the following equation:

$$t_{Absence\_delay} = \frac{19V \times C_{BAT\_}}{I_{BAT}}$$

where  $l_{BAT}$  is the 3.9µA BAT\_ quiescent current (due to a 5M $\Omega$  internal resistor), and  $C_{BAT}$  is the capacitance from BAT\_ to GND. When  $C_{BAT}$  = 1µF, tabsence\_delay corresponds to a 5s time constant. If this time is unacceptable, use a smaller capacitance or connect a resistor or current sink from BAT\_ to GND.

#### Layout

The MAX1538 selector fits in a very small layout. Ensure that C1 is placed close to  $V_{DD}$  and GND. Connect the paddle to GND directly under the IC. A complete layout example is shown in Figure 10.

Because BATA and BATB are high-impedance nodes, prevent leakage current between BATA/BATB and other high-voltage sources by carefully routing traces. Note that flux remaining on the board can significantly contribute to leakage current. See the *Leakage Current into BAT\_* section.

Minimize parasitic inductance in the BATA and BATB path to reduce inductive kick during battery disconnect. This reduces the capacitance requirement at BATA and BATB.

### Pin Configuration

### **Chip Information**

TRANSISTOR COUNT: 5431

PROCESS: BICMOS

20 \_\_\_\_\_\_\_/**N**/**X**|/**V**

Figure 10. MAX1538 Layout Example

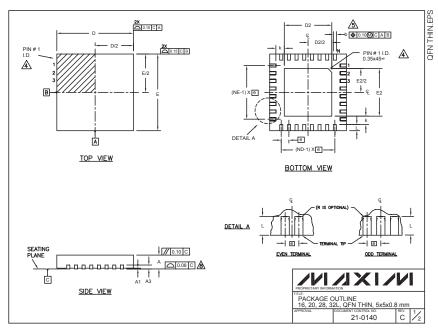

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

|                                                                            |                                                                                                     |                                                                                                 |                                                               | CC                                                                | OMMC                                                                                                       | N DIME                                                           | NSIO                                                                  | NS                                                                        |                                                |                                        |                                          |                             |      | Е         | XPOS       | SED P  | AD V | ARIAT         | LIONS | 5    |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------|----------------------------------------|------------------------------------------|-----------------------------|------|-----------|------------|--------|------|---------------|-------|------|

| PKG.                                                                       |                                                                                                     | 16L 5x5                                                                                         |                                                               |                                                                   | 20L 5x5                                                                                                    |                                                                  |                                                                       | 28L 5x5                                                                   | j                                              |                                        | 32L 5x5                                  |                             | l le | KG.       |            | D2     |      |               | E2    |      |

| SYMBOL                                                                     | MIN.                                                                                                | NOM.                                                                                            | MAX.                                                          | MIN.                                                              | NOM.                                                                                                       | MAX.                                                             | MIN.                                                                  | NOM.                                                                      | MAX.                                           | MIN.                                   | NOM.                                     | MAX.                        | ]  0 | ODES      | MIN.       | NOM.   | MAX. | MIN.          | NOM.  | MAX. |

| Α                                                                          | 0.70                                                                                                | 0.75                                                                                            | 0.80                                                          | 0.70                                                              | 0.75                                                                                                       | 0.80                                                             | 0.70                                                                  | 0.75                                                                      | 0.80                                           | 0.70                                   | 0.75                                     | 0.80                        | T    | 1655-1    | 3.00       | 3.10   | 3.20 | 3.00          | 3.10  | 3.20 |

| A1                                                                         | 0                                                                                                   | 0.02                                                                                            | 0.05                                                          | 0                                                                 | 0.02                                                                                                       | 0.05                                                             | 0                                                                     | 0.02                                                                      | 0.05                                           | 0                                      | 0.02                                     | 0.05                        |      | 2055-2    |            | 3.10   |      | 3.00          | 3.10  | 3.20 |

| A3                                                                         |                                                                                                     | 0.20 REF                                                                                        |                                                               |                                                                   | 0.20 REI                                                                                                   |                                                                  |                                                                       | 0.20 RE                                                                   | F.                                             | -                                      | 0.20 REF                                 |                             |      | 2855-1    |            |        |      | 3.15          |       | 3.35 |

| ь                                                                          | 0.25                                                                                                | 0.30                                                                                            | 0.35                                                          | 0.25                                                              | 0.30                                                                                                       | 0.35                                                             | 0.20                                                                  | 0.25                                                                      | 0.30                                           | 0.20                                   | 0.25                                     | 0.30                        | I —  | 2855-2    |            | 2.70   |      | 2.60          |       | 2.80 |