##

### **3W Mono/Stereo BTL Audio Power Amplifiers** with Shutdown

#### **General Description**

The MAX9710/MAX9711 are stereo/mono 3W bridge-tied load (BTL) audio power amplifiers. These devices are PC99/01 compliant, operate from a single 4.5V to 5.5V supply, and feature an industry-leading 100dB PSRR, which allows these devices to operate from noisy supplies without additional, costly power-supply conditioning. An ultra-low 0.005% THD+N ensures clean, low-distortion amplification of the audio signal while click-and-pop suppression eliminates audible transients on power and shutdown cycles. Power-saving features include low 2mV VOS (minimizing DC current drain through the speakers), low 7mA supply current, and a 0.5µA shutdown mode. A MUTE function allows the outputs to be quickly enabled or disabled.

These devices include thermal overload protection, are specified over the extended -40°C to +85°C temperature range, and are supplied in thermally efficient packages. The MAX9710 is available in a 20-pin thin QFN package (5mm  $\times$  5mm  $\times$  0.8mm). The MAX9711 is available in a 12-pin thin QFN package (4mm × 4mm × 0.8mm).

#### **Applications**

Notebook PCs Two-Way Radios Flat-Panel TVs General-Purpose Audio Flat-Panel PC Displays **Powered Speakers**

## **Features**

- ♦ 3W into 3Ω (1% THD+N)

- ♦ 4W into 3Ω (10% THD+N)

- ♦ Industry-Leading, Ultra-High 100dB PSRR

- ♦ PC99/01 Compliant

- ♦ Click-and-Pop Suppression

- ♦ Low 0.005% THD+N

- ♦ Low Quiescent Current: 7mA

- ♦ Low-Power Shutdown Mode: 0.5µA

- **♦ MUTE Function**

- ♦ Tiny 20-Pin Thin QFN (5mm × 5mm × 0.8mm)

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE     | AMP    |

|------------|----------------|-----------------|--------|

| MAX9710ETP | -40°C to +85°C | 20-Thin QFN-EP* | Stereo |

| MAX9711ETC | -40°C to +85°C | 12-Thin QFN-EP* | Mono   |

<sup>\*</sup>EP = Exposed pad.

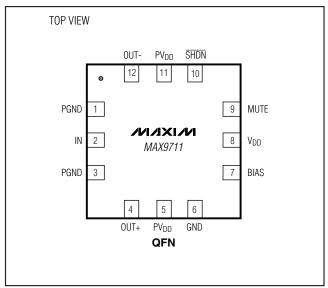

#### **Pin Configurations**

#### TOP VIFW 00TE 18 INL 15 **PGND** SHDN BIAS 14 MIXIM N.C 13 N.C. MAX9710 MUTE 4 12 $V_{DD}$ INR 5 PGND 10 **TOFN** Pin Configurations continued at end of data sheet.

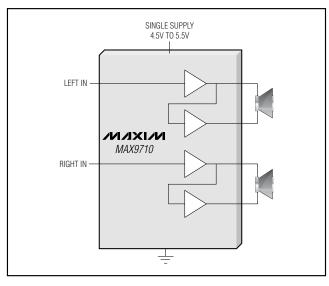

### Simplified Block Diagram

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND, PGND             | +6V                              | 20   |

|------------------------------------------|----------------------------------|------|

| PV <sub>DD</sub> to V <sub>DD</sub>      | ±0.3V                            | Оре  |

| PGND to GND                              | ±0.3V                            | Stor |

| All Other Pins to GND                    | 0.3V to (V <sub>DD</sub> + 0.3V) | Juno |

| Continuous Input Current (into any pin   |                                  | Lea  |

| except power supply and output pins)     | ±20mA                            |      |

| Continuous Power Dissination (TA = ±70°C |                                  |      |

12-Pin Thin QFN (derate 16.9mW/°C above +70°C) ....1349mW

20-Pin Thin QFN (derate 20.8mW/°C above +70°C) ....1667mW

Operating Temperature Range ....-40°C to +85°C

Storage Temperature Range ....-65°C to +150°C

Junction Temperature ....+150°C

Lead Temperature (soldering, 10s) ....+300°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = PV_{DD} = 5.0V, V_{GND} = V_{PGND} = V_{MUTE} = 0V, V_{\overline{SHDN}} = 5V, R_{IN} = R_F = 15k\Omega, R_L = \infty. T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                               | SYMBOL                            | CONDITIONS                                                        |                                                      | MIN  | TYP   | MAX  | UNITS |  |

|-----------------------------------------|-----------------------------------|-------------------------------------------------------------------|------------------------------------------------------|------|-------|------|-------|--|

| Supply Voltage Range                    | V <sub>DD</sub> /PV <sub>DD</sub> | Inferred from PSRR test                                           |                                                      | 4.5  |       | 5.5  | V     |  |

| Quiescent Supply Current                | 1                                 | MAX9710<br>MAX9711                                                |                                                      |      | 12    | 30   | mA    |  |

| (I <sub>VDD</sub> + I <sub>PVDD</sub> ) | lDD                               |                                                                   |                                                      |      | 7     | 17   |       |  |

| Shutdown Supply Current                 | ISHDN                             | SHDN = GND                                                        |                                                      |      | 0.5   | 30   | μΑ    |  |

| Turn On Time                            | to                                | $C_{BIAS} = 1 \mu F (10\% \text{ of }$                            | $C_{BIAS} = 1\mu F (10\% \text{ of final value})$    |      | 300   |      | ma    |  |

| Turn-On Time                            | ton                               | $C_{BIAS} = 0.1 \mu F (10\% c)$                                   | $C_{BIAS} = 0.1 \mu F (10\% \text{ of final value})$ |      | 30    |      | ms    |  |

| Thermal Shutdown Threshold              |                                   |                                                                   |                                                      |      | 160   |      | °C    |  |

| Thermal Shutdown Hysteresis             |                                   |                                                                   |                                                      |      | 15    |      | °C    |  |

| OUTPUT AMPLIFIERS                       |                                   |                                                                   |                                                      |      |       |      |       |  |

| Output Offset Voltage                   | Vos                               | V <sub>OUT_+</sub> - V <sub>OUT</sub> , A <sub>V</sub> :          | = 2                                                  |      | ±2    | ±14  | mV    |  |

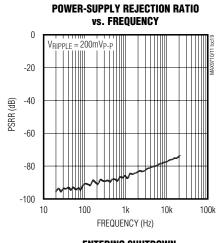

|                                         |                                   | V <sub>RIPPLE</sub> = 200mV <sub>P-P</sub><br>(Note 2)            | $V_{DD} = 4.5V \text{ to } 5.5V$                     | 82   | 100   |      |       |  |

| Power-Supply Rejection Ratio            | PSRR                              |                                                                   | f = 1kHz                                             |      | 87    |      | dB    |  |

|                                         |                                   |                                                                   | f = 20kHz                                            |      | 74    |      |       |  |

| Output Power                            | Pout                              | $f_{IN} = 1kHz,$<br>THD+N < 1%                                    | $R_L = 8\Omega$                                      | 1.1  | 1.4   |      | W     |  |

|                                         |                                   |                                                                   | $R_L = 4\Omega$                                      |      | 2.6   |      |       |  |

|                                         |                                   |                                                                   | $R_L = 3\Omega$                                      |      | 3     |      |       |  |

| Total Harmonic Distortion Plus          | THD+N                             | f <sub>IN</sub> = 1kHz, BW =                                      | $P_{OUT} = 1.2W, R_L = 8\Omega$                      |      | 0.005 |      | %     |  |

| Noise                                   | IUD+IV                            | 22Hz to 22kHz                                                     | $P_{OUT} = 2W, 4\Omega$                              |      | 0.01  |      | 1 %   |  |

| Signal-to-Noise Ratio                   | SNR                               | $R_L = 8\Omega$ , $V_{OUT} = 2.8V_{RMS}$ , $BW = 22Hz$ to $22kHz$ |                                                      |      | 95    |      | dB    |  |

| Slew Rate                               | SR                                |                                                                   |                                                      |      | 1.6   |      | V/µs  |  |

| Maximum Capacitive Load Drive           | CL                                | No sustained oscillations                                         |                                                      |      | 1     |      | nF    |  |

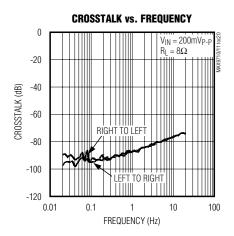

| Crosstalk                               |                                   | f <sub>IN</sub> = 10kHz                                           |                                                      |      | 77    |      | dB    |  |

| BIAS VOLTAGE (BIAS)                     |                                   |                                                                   |                                                      |      |       |      |       |  |

| BIAS Voltage                            | V <sub>BIAS</sub>                 |                                                                   |                                                      | 2.35 | 2.5   | 2.65 | V     |  |

| Output Resistance                       | RBIAS                             |                                                                   |                                                      |      | 50    |      | kΩ    |  |

| DIGITAL INPUTS (MUTE, SHDN)             |                                   |                                                                   |                                                      |      |       |      |       |  |

| Input Voltage High                      | VIH                               |                                                                   |                                                      | 2    |       |      | V     |  |

| Input Voltage Low                       | V <sub>IL</sub>                   |                                                                   |                                                      |      |       | 0.8  | V     |  |

| Input Leakage Current                   | I <sub>IN</sub>                   |                                                                   |                                                      |      |       | ±1   | μΑ    |  |

Note 1: All devices are 100% production tested at +25°C. All temperature limits are guaranteed by design.

Note 2: PSSR is specified with the amplifier inputs connected to GND through RIN and CIN.

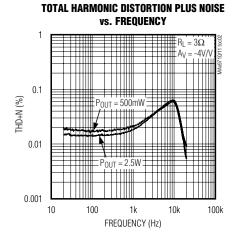

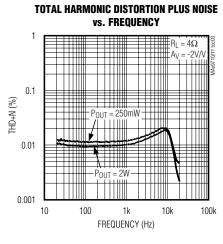

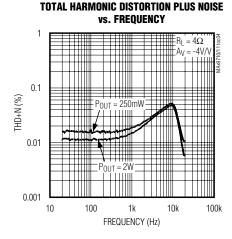

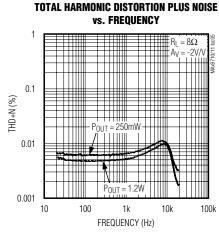

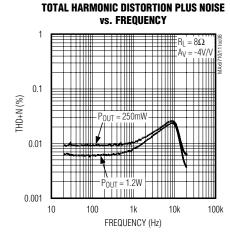

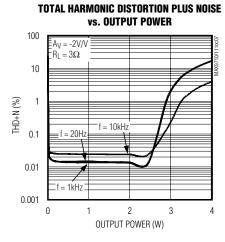

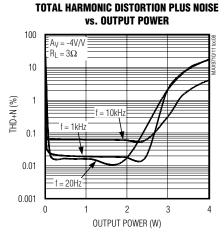

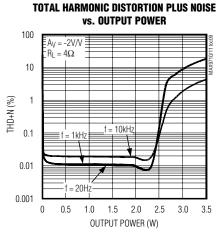

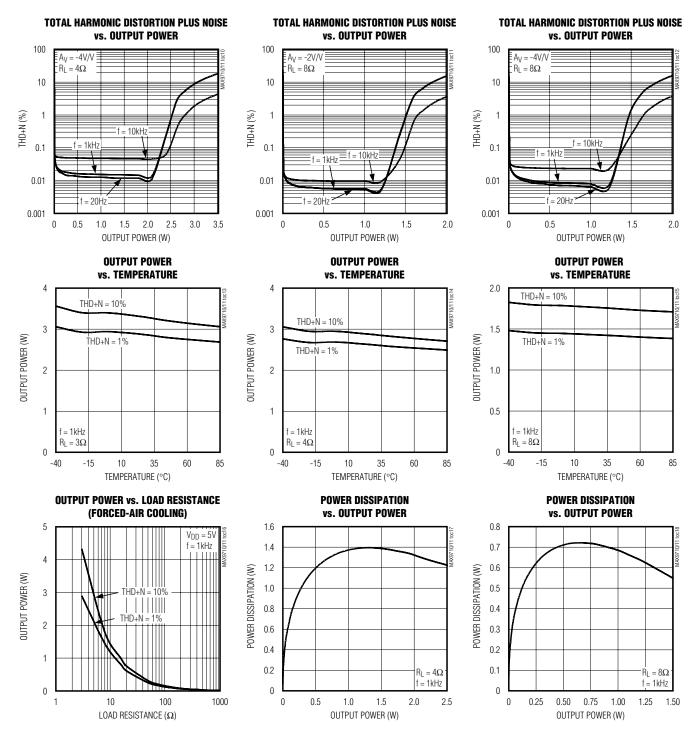

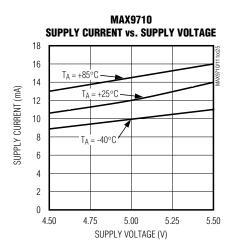

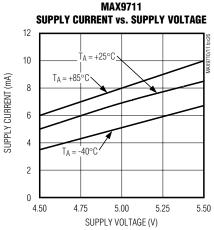

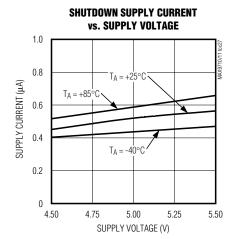

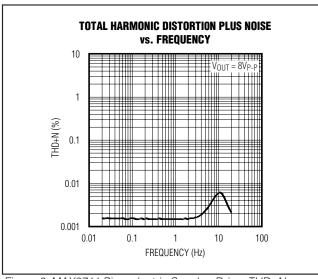

### Typical Operating Characteristics

$(V_{DD} = 5V, THD+N \text{ measurement bandwidth} = 22Hz \text{ to } 22kHz, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

##

#### Typical Operating Characteristics (continued)

$(V_{DD} = 5V, THD+N \text{ measurement bandwidth} = 22Hz \text{ to } 22kHz, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### Typical Operating Characteristics (continued)

$(V_{DD} = 5V, THD+N \text{ measurement bandwidth} = 22Hz \text{ to } 22kHz, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### \_Typical Operating Characteristics (continued)

$(V_{DD} = 5V, THD+N \text{ measurement bandwidth} = 22Hz \text{ to } 22kHz, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

#### **Pin Description**

| P             | IN      |                  | FUNCTION                                                            |  |  |

|---------------|---------|------------------|---------------------------------------------------------------------|--|--|

| MAX9710       | MAX9711 | NAME             | FUNCTION                                                            |  |  |

| 1             | _       | INL              | Left-Channel Input                                                  |  |  |

| 2             | 7       | BIAS             | DC Bias Bypass. See BIAS Capacitor section for capacitor selection. |  |  |

| 3, 10, 13, 16 | _       | N.C.             | No Connection. Not internally connected.                            |  |  |

| 4             | 9       | MUTE             | Active-High Mute Input                                              |  |  |

| 5             | _       | INR              | Right-Channel Input                                                 |  |  |

| 6, 11, 15, 20 | 1, 3    | PGND             | Power Ground                                                        |  |  |

| 7             | _       | OUTR+            | Right-Channel Bridged Amplifier Positive Output                     |  |  |

| 8, 18         | 5, 11   | PV <sub>DD</sub> | Output Amplifier Power Supply                                       |  |  |

| 9             | _       | OUTR-            | Right-Channel Bridged Amplifier Negative Output                     |  |  |

| 12            | 8       | V <sub>DD</sub>  | Power Supply                                                        |  |  |

| 14            | 10      | SHDN             | Active-Low Shutdown. Connect SHDN to VDD for normal operation.      |  |  |

| 17            | _       | OUTL-            | Left-Channel Bridged Amplifier Negative Output                      |  |  |

| 19            | _       | OUTL+            | Left-Channel Bridged Amplifier Positive Output                      |  |  |

| _             | 2       | IN               | Amplifier Input                                                     |  |  |

| _             | 6       | GND              | Ground                                                              |  |  |

| _             | 12      | OUT-             | Bridged Amplifier Negative Output                                   |  |  |

| _             | 4       | OUT+             | Bridged Amplifier Positive Output                                   |  |  |

| _             | _       | EP               | Exposed Pad. Connect to ground plane.                               |  |  |

#### **Detailed Description**

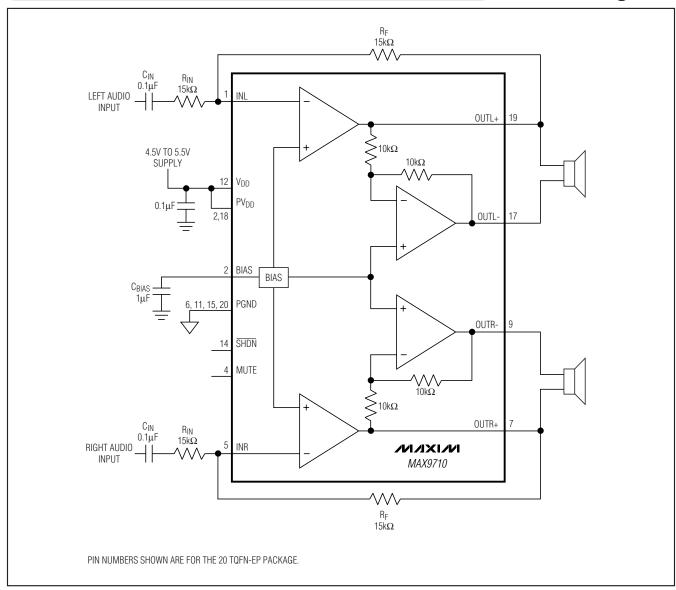

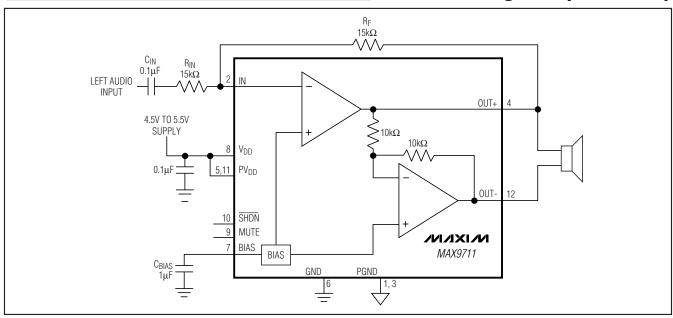

The MAX9710/MAX9711 are 3W BTL speaker amplifiers. The MAX9710 is a stereo speaker amplifier, while the MAX9711 is a mono speaker amplifier. Both devices feature a low-power shutdown mode, MUTE mode, and comprehensive click-and-pop suppression. These devices consist of high output-current op amps configured as BTL amplifiers (see *Functional Diagrams*). The device gain is set by RF and RIN.

#### BIAS

These devices operate from a single 5V supply and feature an internally generated, power-supply-independent, common-mode bias voltage of 2.5V referenced to ground. BIAS provides both click-and-pop suppression and sets the DC bias level for the audio outputs. BIAS is internally connected to the noninverting input of each speaker amplifier (see *Functional Diagrams*). Choose the value of the bypass capacitor as described in the *BIAS Capacitor* section. No external load should be applied to BIAS. Any load lowers the BIAS voltage, affecting the overall performance of the device.

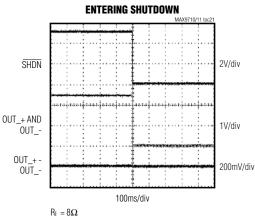

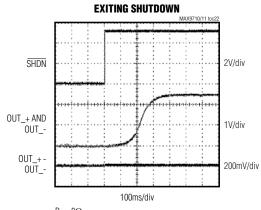

#### Shutdown

The MAX9710/MAX9711 feature a  $0.5\mu A$  low-power shutdown mode that reduces quiescent current consumption. Pulling  $\overline{SHDN}$  low disables the device's bias circuitry, the amplifier outputs are actively pulled low, and BIAS is driven to GND. Connect  $\overline{SHDN}$  to  $V_{DD}$  for normal operation.

#### MUTE

Both devices feature a clickless/popless MUTE mode. When the device is muted, the input disconnects from the amplifier. MUTE only affects the power amplifiers and does not shut down the device. Drive MUTE high to mute the device. Drive MUTE low for normal operation.

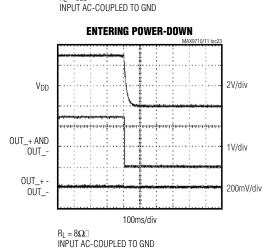

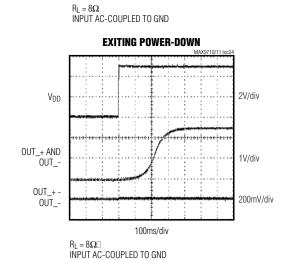

#### **Click-and-Pop Suppression**

The MAX9710/MAX9711 feature Maxim's comprehensive click-and-pop suppression. During startup, the common-mode bias voltage of the amplifiers slowly ramps to the DC bias point using an S-shaped waveform. When entering shutdown, the amplifier outputs are actively driven low simultaneously. This scheme minimizes the energy present in the audio band.

For optimum click-and-pop suppression, choose:

RIN x CIN < RBIAS x CBIAS

where RBIAS =  $50k\Omega$ .

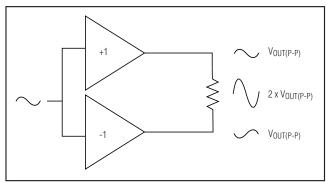

Figure 1. Bridge-Tied Load Configuration

### **Applications Information**

#### **BTL Amplifier**

The MAX9710/MAX9711 are designed to drive a load differentially, a configuration referred to as BTL. The BTL configuration (Figure 1) offers advantages over the single-ended configuration, where one side of the load is connected to ground. Driving the load differentially doubles the output voltage compared to a single-ended amplifier under similar conditions. Thus, the differential gain of the device is twice the closed-loop gain of the input amplifier. The effective gain is given by:

$$A_{VD} = 2 \times \frac{R_F}{R_{IN}}$$

Substituting 2 x VOUT(P-P) for VOUT(P-P) into the following equations yields four times the output power due to doubling of the output voltage:

$$V_{RMS} = \frac{V_{OUT(P-P)}}{2\sqrt{2}}$$

$$P_{OUT} = \frac{V_{RMS}^2}{R_L}$$

Since the differential outputs are biased at midsupply, there is no net DC voltage across the load. This eliminates the need for DC-blocking capacitors required for single-ended amplifiers. These capacitors can be large, expensive, consume board space, and degrade low-frequency performance.

#### **Power Dissipation and Heat Sinking**

Under normal operating conditions, the MAX9710/MAX9711 dissipate a significant amount of power. The maximum power dissipation for each package is given in the *Absolute Maximum Ratings* section under Continuous Power Dissipation or can be calculated by the following equation:

$$P_{\text{DISSPKG}(MAX)} = \frac{T_{\text{J}(MAX)} - T_{\text{A}}}{\theta_{\text{JA}}}$$

where  $T_{J(MAX)}$  is +150°C,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the reciprocal of the derating factor in °C/W as specified in the *Absolute Maximum Ratings* section. For example,  $\theta_{JA}$  of the 20-pin thin QFN package is 48.1°C/W.

The increase in power delivered by the BTL configuration directly results in an increase in internal power dissipation over the single-ended configuration. The maximum power dissipation for a given V<sub>DD</sub> and load is given by the following equation:

$$P_{\text{DISS(MAX)}} = \frac{2V_{\text{DD}}^2}{\pi^2 R_{\text{I}}}$$

If the power dissipation for a given application exceeds the maximum allowed for a given package, either reduce V<sub>DD</sub>, increase load impedance, decrease the ambient temperature, or add heat sinking to the device (see *Layout and Grounding* section). Large output, supply, and ground PC board traces improve the maximum power dissipation in the package.

Thermal-overload protection limits total power dissipation in the MAX9710/MAX9711. When the junction temperature exceeds +160°C, the thermal protection circuitry disables the amplifier output stage. The amplifiers are enabled once the junction temperature cools by 15°C. A pulsing output under continuous thermal-overload conditions results as the device heats and cools.

#### Component Selection

#### Gain-Setting Resistors

External feedback components set the gain of both devices. Resistors  $R_{\text{F}}$  and  $R_{\text{IN}}$  (Functional Diagrams) set the gain of the amplifier as follows:

$$A_{VD} = 2 \times \frac{R_F}{R_{IN}}$$

#### Input Filter

The input capacitor ( $C_{IN}$ ), in conjunction with  $R_{IN}$ , forms a highpass filter that removes the DC bias from an incoming signal. The AC-coupling capacitor allows the amplifier to bias the signal to an optimum DC level. Assuming zero-source impedance, the -3dB point of the highpass filter is given by:

$$f_{-3dB} = \frac{1}{2\pi R_{IN} C_{IN}}$$

For optimum click-and-pop suppression, choose:

where RBIAS =  $50k\Omega$ .

Setting f-3dB too high affects the low-frequency response of the amplifier. Use capacitors with dielectrics that have low-voltage coefficients, such as tantalum or aluminum electrolytic. Capacitors with high-voltage coefficients, such as ceramics, may result in an increase of distortion at low frequencies.

#### **BIAS Capacitor**

BIAS is the output of the internally generated 2.5VDC bias voltage. The BIAS bypass capacitor,  $C_{BIAS}$ , improves PSRR and THD+N by reducing power supply and other noise sources at the common-mode bias node, and also generates the clickless/popless startup DC bias waveform for the speaker amplifiers. Bypass BIAS with a 1µF capacitor to GND. Smaller values of CBIAS produce faster toN/toFF times but may result in increased click/pop levels.

#### Supply Bypassing

Proper power-supply bypassing ensures low-noise, low-distortion performance. Place a 0.1µF ceramic capacitor from V<sub>DD</sub> to PGND. Add additional bulk capacitance as required by the application. Locate the bypass capacitor as close to the device as possible.

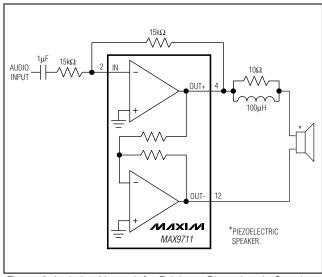

#### Piezoelectric Speaker Driver

Low-profile piezoelectric speakers can provide quality sound for portable electronics. However, piezoelectric speakers typically require large voltage swings (>8VP-P) across the speaker element to produce audible sound pressure levels. The MAX9711 can be configured to drive a piezoelectric speaker with up to 10VP-P while operating from a single 5V supply.

Figure 2 shows the THD+N of the MAX9711 driving a piezoelectric speaker. Note that as frequency increases, the THD+N increases. This is due to the capacitive nature of the piezoelectric speaker; as frequency increases, the speaker impedance decreases, resulting in a larger current draw from the amplifier.

Figure 2. MAX9711 Piezoelectric Speaker Driver THD+N vs. Frequency

The capacitive nature of the piezoelectric speaker may cause the MAX9711 to become unstable. A simple inductor/resistor network in series with the speaker isolates the speaker capacitance from the driver and ensures that the device output sees a resistive load of about  $10\Omega$  at high frequency, thereby maintaining stability (Figure 3).

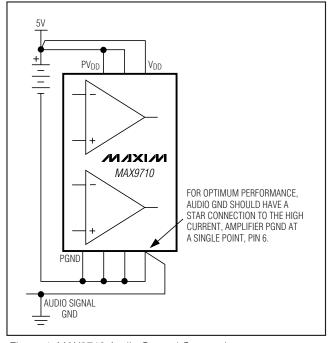

#### **Layout and Grounding**

Good PC board layout is essential for optimizing performance. Use large traces for the power-supply inputs and amplifier outputs to minimize losses due to parasitic trace resistance and route heat away from the device. Good grounding improves audio performance, minimizes crosstalk between channels, and prevents any digital switching noise from coupling into the audio signal.

The MAX9710/MAX9711 thin QFN package features an exposed thermal pad on the underside. This pad lowers the thermal resistance of the package by providing a direct-heat conduction path from the die to the printed circuit board. Connect the exposed pad to the ground plane using multiple vias, if required. For optimum performance, connect to the ground planes as shown in Figure 4.

Figure 3. Isolation Network for Driving a Piezoelectric Speaker

Figure 4. MAX9710 Audio Ground Connection

### Functional Diagrams

### Functional Diagrams (continued)

### Pin Configurations (continued)

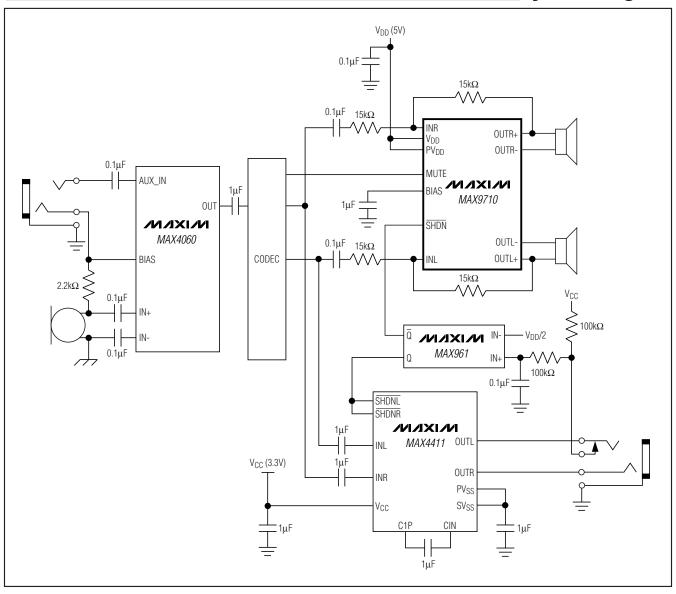

#### System Diagram

### Package Information

For the latest package outline information and land patterns, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 20 TQFN-EP   | T2055-4      | <u>21-0140</u> |

| 12 TQFN-EP   | T1244-4      | <u>21-0139</u> |

### \_Chip Information

MAX9710 TRANSISTOR COUNT: 1172 MAX9711 TRANSISTOR COUNT: 780

PROCESS: BICMOS

#### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION           | PAGES<br>CHANGED |

|--------------------|------------------|-----------------------|------------------|

| 0                  | 4/03             | Initial release       | _                |

| 1                  | 6/08             | Removed TSSOP package | 1, 2, 6, 9, 10   |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.