# MCP2515

## **Stand-Alone CAN Controller With SPI Interface**

### **Features**

- Implements CAN V2.0B at 1 Mb/s:

- 0 8 byte length in the data field

- Standard and extended data and remote frames

- · Receive buffers, masks and filters:

- Two receive buffers with prioritized message storage

- Six 29-bit filters

- Two 29-bit masks

- Data byte filtering on the first two data bytes (applies to standard data frames)

- Three transmit buffers with prioritization and abort features

- High-speed SPI Interface (10 MHz):

- SPI modes 0,0 and 1,1

- One-shot mode ensures message transmission is attempted only one time

- · Clock out pin with programmable prescaler:

- Can be used as a clock source for other device(s)

- Start-of-Frame (SOF) signal is available for monitoring the SOF signal:

- Can be used for time-slot-based protocols and/or bus diagnostics to detect early bus degredation

- · Interrupt output pin with selectable enables

- Buffer Full output pins configurable as:

- Interrupt output for each receive buffer

- General purpose output

- Request-to-Send (RTS) input pins individually configurable as:

- Control pins to request transmission for each transmit buffer

- General purpose inputs

- · Low-power CMOS technology:

- Operates from 2.7V 5.5V

- 5 mA active current (typical)

- 1 µA standby current (typical) (Sleep mode)

- Temperature ranges supported:

- Industrial (I): -40°C to +85°C

- Extended (E): -40°C to +125°C

### **Description**

Microchip Technology's MCP2515 is a stand-alone Controller Area Network (CAN) controller that implements the CAN specification, version 2.0B. It is capable of transmitting and receiving both standard and extended data and remote frames. The MCP2515 has two acceptance masks and six acceptance filters that are used to filter out unwanted messages, thereby reducing the host MCUs overhead. The MCP2515 interfaces with microcontrollers (MCUs) via an industry standard Serial Peripheral Interface (SPI).

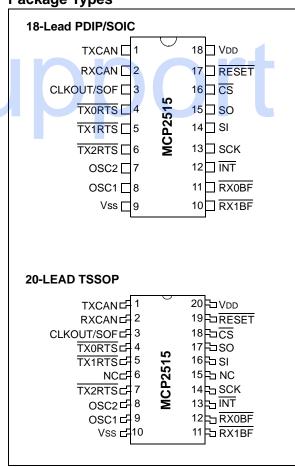

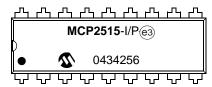

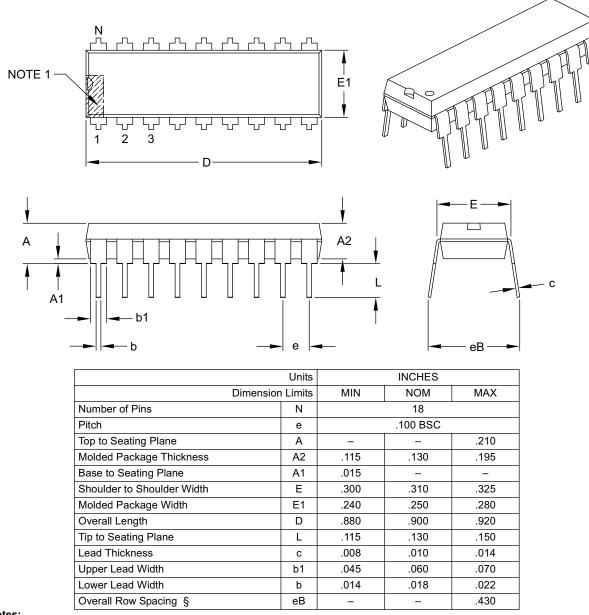

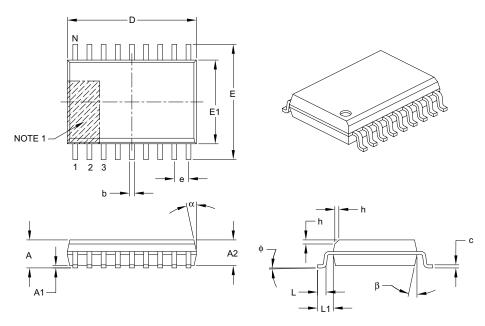

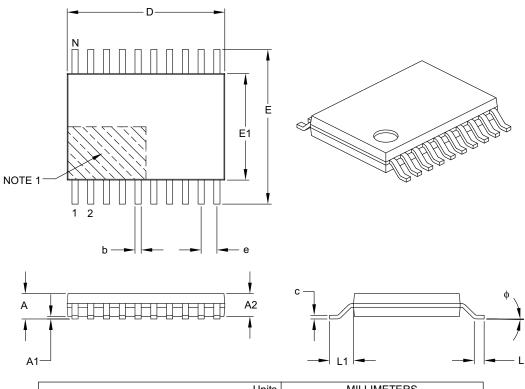

### **Package Types**

## MCP2515

NOTES:

### 1.0 DEVICE OVERVIEW

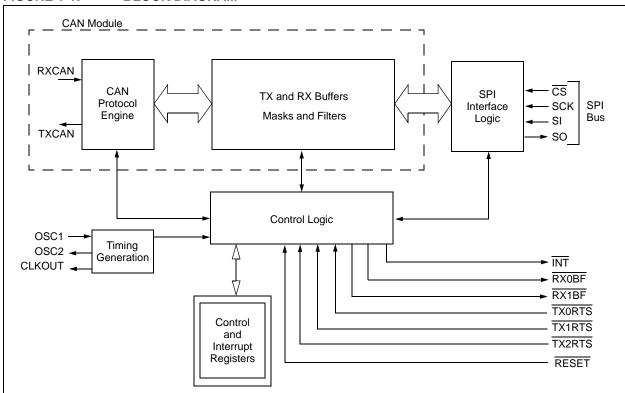

The MCP2515 is a stand-alone CAN controller developed to simplify applications that require interfacing with a CAN bus. A simple block diagram of the MCP2515 is shown in Figure 1-1. The device consists of three main blocks:

- The CAN module, which includes the CAN protocol engine, masks, filters, transmit and receive buffers.

- 2. The control logic and registers that are used to configure the device and its operation.

- 3. The SPI protocol block.

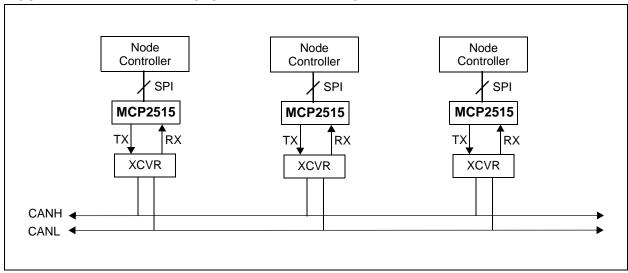

An example system implementation using the device is shown in Figure 1-2.

### 1.1 CAN Module

The CAN module handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate message buffer and control registers. Transmission is initiated by using control register bits via the SPI interface or by using the transmit enable pins. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against the user-defined filters to see if it should be moved into one of the two receive buffers.

### 1.2 Control Logic

The control logic block controls the setup and operation of the MCP2515 by interfacing to the other blocks in order to pass information and control.

Interrupt pins are provided to allow greater system flexibility. There is one multi-purpose interrupt pin (as well as specific interrupt pins) for each of the receive registers that can be used to indicate a valid message has been received and loaded into one of the receive buffers. Use of the specific interrupt pins is optional. The general purpose interrupt pin, as well as status registers (accessed via the SPI interface), can also be used to determine when a valid message has been received.

Additionally, there are three pins available to initiate immediate transmission of a message that has been loaded into one of the three transmit registers. Use of these pins is optional, as initiating message transmissions can also be accomplished by utilizing control registers, accessed via the SPI interface.

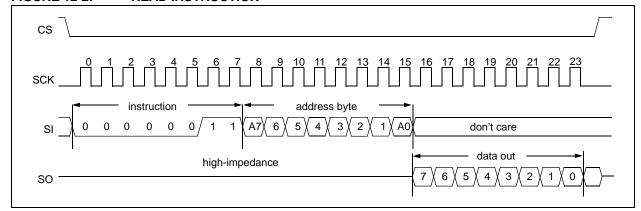

#### 1.3 SPI Protocol Block

The MCU interfaces to the device via the SPI interface. Writing to, and reading from, all registers is accomplished using standard SPI read and write commands, in addition to specialized SPI commands.

FIGURE 1-1: BLOCK DIAGRAM

FIGURE 1-2: EXAMPLE SYSTEM IMPLEMENTATION

TABLE 1-1: PINOUT DESCRIPTION

| Name   | PDIP/SOIC<br>Pin # | TSSOP<br>Pin # | I/O/P<br>Type | Description                                                                 | Alternate Pin Function                                           |

|--------|--------------------|----------------|---------------|-----------------------------------------------------------------------------|------------------------------------------------------------------|

| TXCAN  | 1                  | 1              | 0             | Transmit output pin to CAN bus                                              | _                                                                |

| RXCAN  | 2                  | 2              | 1             | Receive input pin from CAN bus                                              | _                                                                |

| CLKOUT | 3                  | 3              | 0             | Clock output pin with programmable prescaler                                | Start-of-Frame signal                                            |

| TX0RTS | 4                  | 4              | I             | Transmit buffer TXB0 request-to-send. 100 $k\Omega$ internal pull-up to VDD | General purpose digital input.<br>100 kΩ internal pull-up to VDD |

| TX1RTS | 5                  | 5              | I             | Transmit buffer TXB1 request-to-send. 100 $k\Omega$ internal pull-up to VDD | General purpose digital input.<br>100 kΩ internal pull-up to VDD |

| TX2RTS | 6                  | 7              | I             | Transmit buffer TXB2 request-to-send. 100 $k\Omega$ internal pull-up to VDD | General purpose digital input.<br>100 kΩ internal pull-up to VDD |

| OSC2   | 7                  | 8              | 0             | Oscillator output                                                           | _                                                                |

| OSC1   | 8                  | 9              | I             | Oscillator input                                                            | External clock input                                             |

| Vss    | 9                  | 10             | Р             | Ground reference for logic and I/O pins                                     | _                                                                |

| RX1BF  | 10                 | 11             | 0             | Receive buffer RXB1 interrupt pin or general purpose digital output         | General purpose digital output                                   |

| RX0BF  | 11                 | 12             | 0             | Receive buffer RXB0 interrupt pin or general purpose digital output         | General purpose digital output                                   |

| ĪNT    | 12                 | 13             | 0             | Interrupt output pin                                                        | _                                                                |

| SCK    | 13                 | 14             | I             | Clock input pin for SPI interface                                           | _                                                                |

| SI     | 14                 | 16             | I             | Data input pin for SPI interface                                            | _                                                                |

| SO     | 15                 | 17             | 0             | Data output pin for SPI interface                                           | _                                                                |

| CS     | 16                 | 18             | I             | Chip select input pin for SPI interface                                     | _                                                                |

| RESET  | 17                 | 19             | ı             | Active low device reset input                                               | _                                                                |

| VDD    | 18                 | 20             | Р             | Positive supply for logic and I/O pins                                      | _                                                                |

| NC     |                    | 6,15           | _             | No internal connection                                                      |                                                                  |

**Note:** Type Identification: I = Input; O = Output; P = Power

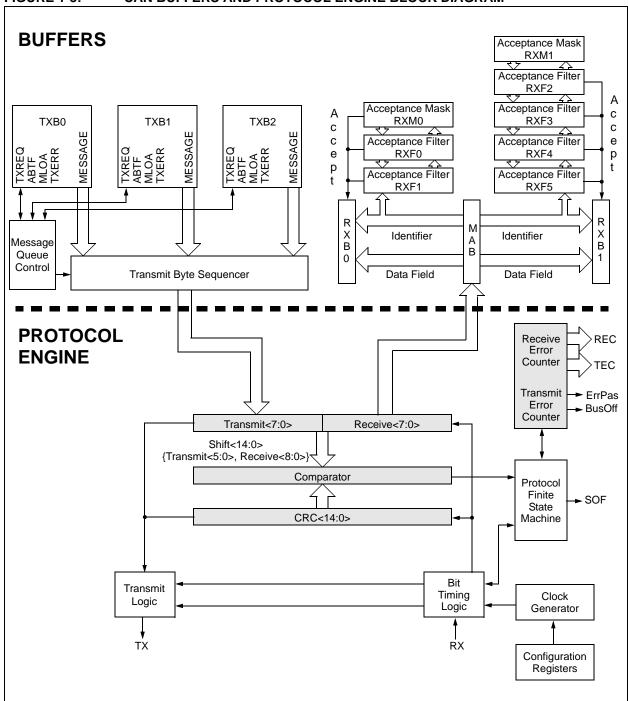

### 1.4 Transmit/Receive Buffers/Masks/ Filters

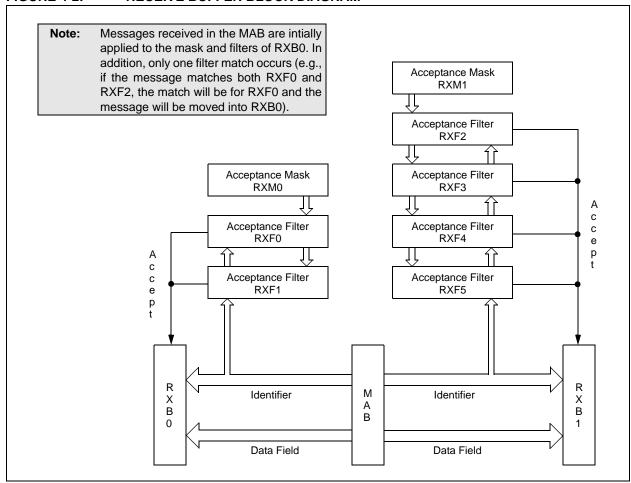

The MCP2515 has three transmit and two receive buffers, two acceptance masks (one for each receive buffer) and a total of six acceptance filters. Figure 1-3 shows a block diagram of these buffers and their connection to the protocol engine.

FIGURE 1-3: CAN BUFFERS AND PROTOCOL ENGINE BLOCK DIAGRAM

### 1.5 CAN Protocol Engine

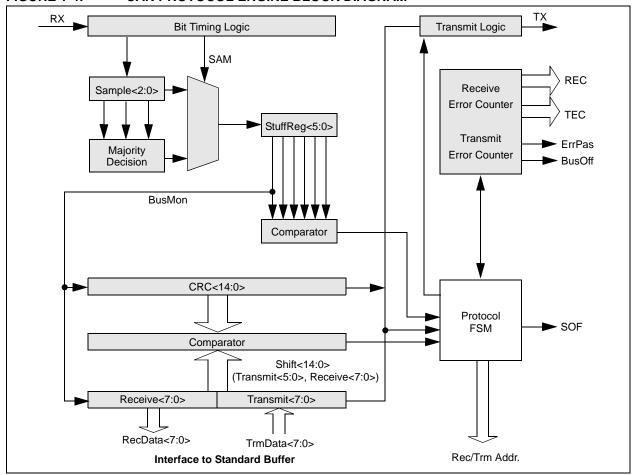

The CAN protocol engine combines several functional blocks, shown in Figure 1-4 and described below.

## 1.5.1 PROTOCOL FINITE STATE MACHINE

The heart of the engine is the Finite State Machine (FSM). The FSM is a sequencer that controls the sequential data stream between the TX/RX shift register, the CRC register and the bus line. The FSM also controls the Error Management Logic (EML) and the parallel data stream between the TX/RX shift registers and the buffers. The FSM ensures that the processes of reception, arbitration, transmission and error-signaling are performed according to the CAN protocol. The automatic retransmission of messages on the bus line is also handled by the FSM.

#### 1.5.2 CYCLIC REDUNDANCY CHECK

The Cyclic Redundancy Check register generates the Cyclic Redundancy Check (CRC) code, which is transmitted after either the Control Field (for messages with 0 data bytes) or the Data Field and is used to check the CRC field of incoming messages.

#### 1.5.3 ERROR MANAGEMENT LOGIC

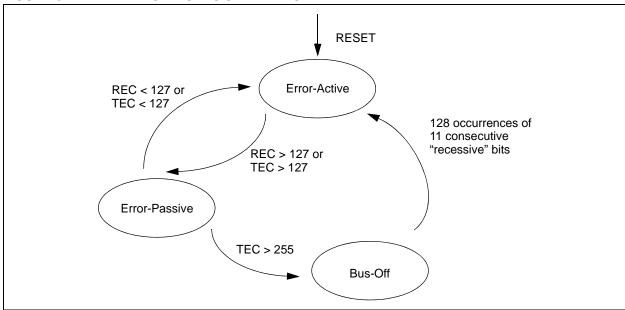

The Error Management Logic (EML) is responsible for the fault confinement of the CAN device. Its two counters, the Receive Error Counter (REC) and the Transmit Error Counter (TEC), are incremented and decremented by commands from the bit stream processor. Based on the values of the error counters, the CAN controller is set into the states error-active, error-passive or bus-off.

#### 1.5.4 BIT TIMING LOGIC

The Bit Timing Logic (BTL) monitors the bus line input and handles the bus-related bit timing according to the CAN protocol. The BTL synchronizes on a recessive-to-dominant bus transition at Start-of-Frame (hard synchronization) and on any further recessive-to-dominant bus line transition if the CAN controller itself does not transmit a dominant bit (resynchronization). The BTL also provides programmable time segments to compensate for the propagation delay time, phase shifts and to define the position of the sample point within the bit time. The programming of the BTL depends on the baud rate and external physical delay times.

FIGURE 1-4: CAN PROTOCOL ENGINE BLOCK DIAGRAM

### 2.0 CAN MESSAGE FRAMES

The MCP2515 supports standard data frames, extended data frames and remote frames (standard and extended), as defined in the CAN 2.0B specification.

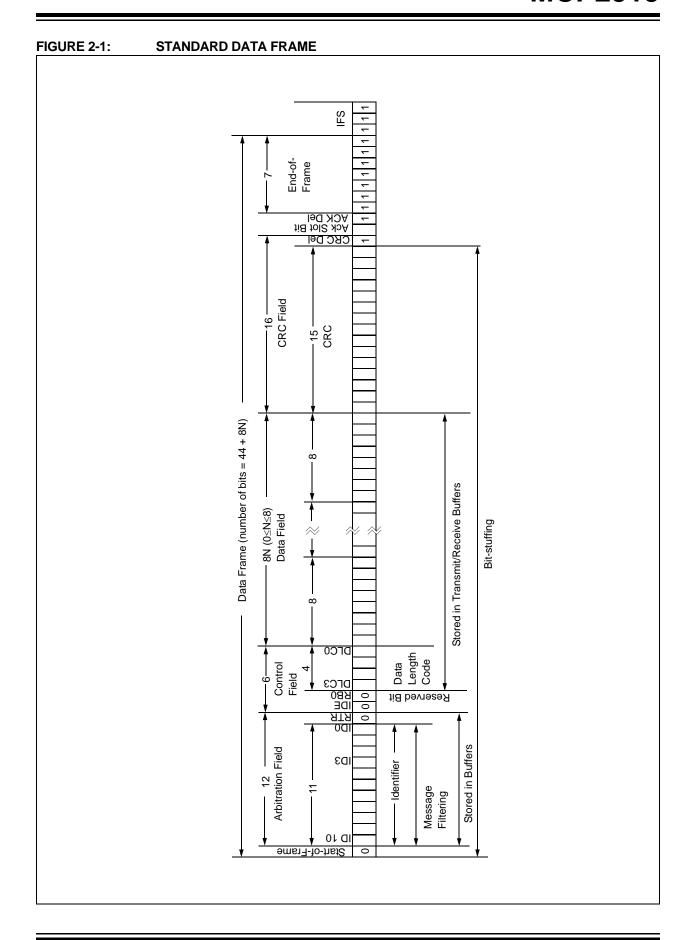

#### 2.1 Standard Data Frame

The CAN standard data frame is shown in Figure 2-1. As with all other frames, the frame begins with a Start-Of-Frame (SOF) bit, which is of the dominant state and allows hard synchronization of all nodes.

The SOF is followed by the arbitration field, consisting of 12 bits: the 11-bit identifier and the Remote Transmission Request (RTR) bit. The RTR bit is used to distinguish a data frame (RTR bit dominant) from a remote frame (RTR bit recessive).

Following the arbitration field is the control field, consisting of six bits. The first bit of this field is the Identifier Extension (IDE) bit, which must be dominant to specify a standard frame. The following bit, Reserved Bit Zero (RB0), is reserved and is defined as a dominant bit by the CAN protocol. The remaining four bits of the control field are the Data Length Code (DLC), which specifies the number of bytes of data (0-8 bytes) contained in the message.

After the control field is the data field, which contains any data bytes that are being sent, and is of the length defined by the DLC (0-8) bytes).

The Cyclic Redundancy Check (CRC) field follows the data field and is used to detect transmission errors. The CRC field consists of a 15-bit CRC sequence, followed by the recessive CRC Delimiter bit.

The final field is the two-bit Acknowledge (ACK) field. During the ACK Slot bit, the transmitting node sends out a recessive bit. Any node that has received an error-free frame acknowledges the correct reception of the frame by sending back a dominant bit (regardless of whether the node is configured to accept that specific message or not). The recessive acknowledge delimiter completes the acknowledge field and may not be overwritten by a dominant bit.

### 2.2 Extended Data Frame

In the extended CAN data frame, shown in Figure 2-2, the SOF bit is followed by the arbitration field, which consists of 32 bits. The first 11 bits are the Most Significant bits (MSb) (Base-ID) of the 29-bit identifier. These 11 bits are followed by the Substitute Remote Request (SRR) bit, which is defined to be recessive. The SRR bit is followed by the IDE bit, which is recessive to denote an extended CAN frame.

It should be noted that if arbitration remains unresolved after transmission of the first 11 bits of the identifier, and one of the nodes involved in the arbitration is sending a standard CAN frame (11-bit identifier), the standard CAN frame will win arbitration due to the assertion of a dominant IDE bit. Also, the SRR bit in an extended CAN frame must be recessive to allow the assertion of a dominant RTR bit by a node that is sending a standard CAN remote frame.

The SRR and IDE bits are followed by the remaining 18 bits of the identifier (Extended ID) and the remote transmission request bit.

To enable standard and extended frames to be sent across a shared network, the 29-bit extended message identifier is split into 11-bit (most significant) and 18-bit (least significant) sections. This split ensures that the IDE bit can remain at the same bit position in both the standard and extended frames.

Following the arbitration field is the six-bit control field. The first two bits of this field are reserved and must be dominant. The remaining four bits of the control field are the DLC, which specifies the number of data bytes contained in the message.

The remaining portion of the frame (data field, CRC field, acknowledge field, end-of-frame and intermission) is constructed in the same way as a standard data frame (see **Section 2.1 "Standard Data Frame"**).

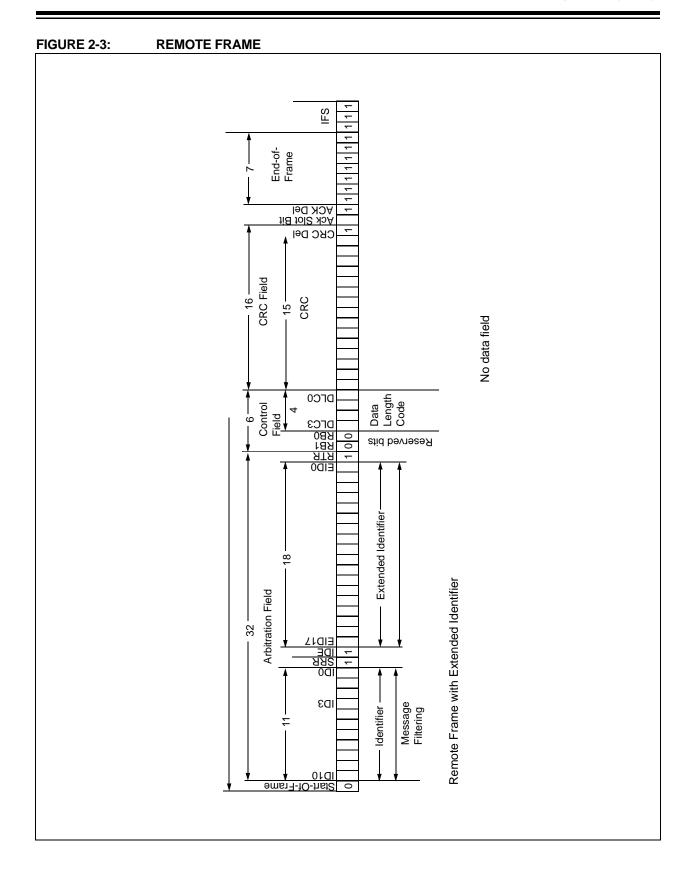

#### 2.3 Remote Frame

Normally, data transmission is performed on an autonomous basis by the data source node (e.g., a sensor sending out a data frame). It is possible, however, for a destination node to request data from the source. To accomplish this, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node will then send a data frame in response to the remote frame request.

There are two differences between a remote frame (shown in Figure 2-3) and a data frame. First, the RTR bit is at the recessive state and, second, there is no data field. In the event of a data frame and a remote frame with the same identifier being transmitted at the same time, the data frame wins arbitration due to the dominant RTR bit following the identifier. In this way, the node that transmitted the remote frame receives the desired data immediately.

### 2.4 Error Frame

An error frame is generated by any node that detects a bus error. An error frame, shown in Figure 2-4, consists of two fields: an error flag field followed by an error delimiter field. There are two types of error flag fields. The type of error flag field sent depends upon the error status of the node that detects and generates the error flag field.

### 2.4.1 ACTIVE ERRORS

If an error-active node detects a bus error, the node interrupts transmission of the current message by generating an active error flag. The active error flag is composed of six consecutive dominant bits. This bit sequence actively violates the bit-stuffing rule. All other stations recognize the resulting bit-stuffing error and, in turn, generate error frames themselves, called error echo flags.

The error flag field, therefore, consists of between six and twelve consecutive dominant bits (generated by one or more nodes). The error delimiter field (eight recessive bits) completes the error frame. Upon completion of the error frame, bus activity returns to normal and the interrupted node attempts to resend the aborted message.

Note: Error echo flags typically occur when a localized disturbance causes one or more (but not all) nodes to send an error flag. The remaining nodes generate error flags in response (echo) to the original error flag.

### 2.4.2 PASSIVE ERRORS

If an error-passive node detects a bus error, the node transmits an error-passive flag followed by the error delimiter field. The error-passive flag consists of six consecutive recessive bits. The error frame for an error-passive node consists of 14 recessive bits. From this it follows that, unless the bus error is detected by an error-active node or the transmitting node, the message will continue transmission because the error-passive flag does not interfere with the bus.

If the transmitting node generates an error-passive flag, it will cause other nodes to generate error frames due to the resulting bit-stuffing violation. After transmission of an error frame, an error-passive node must wait for six consecutive recessive bits on the bus before attempting to rejoin bus communications.

The error delimiter consists of eight recessive bits and allows the bus nodes to restart bus communications cleanly after an error has occurred.

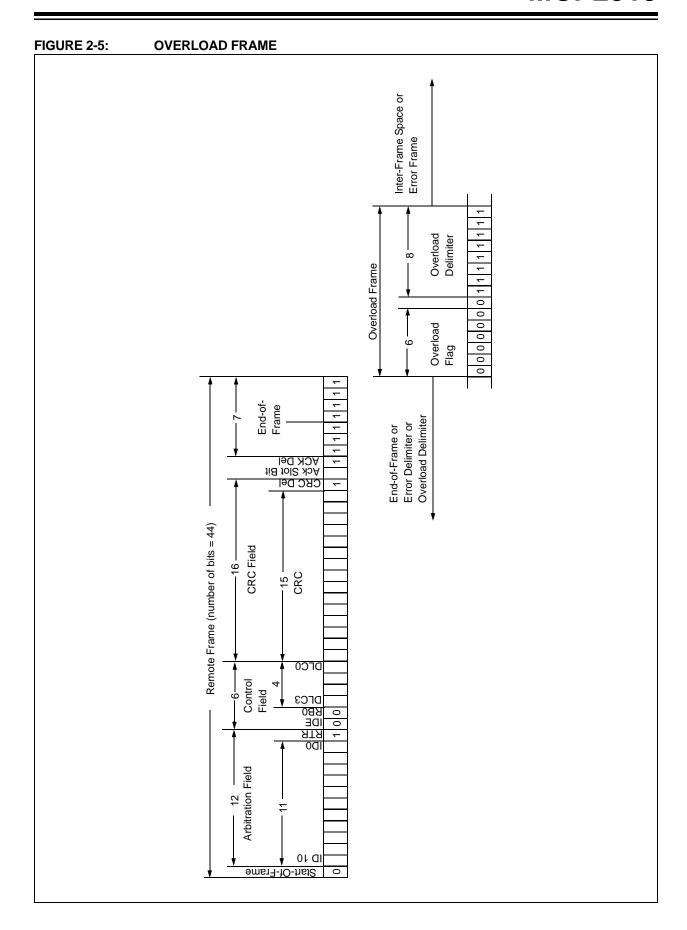

### 2.5 Overload Frame

An overload frame, shown in Figure 2-5, has the same format as an active error frame. An overload frame, however, can only be generated during an interframe space. In this way, an overload frame can be differentiated from an error frame (an error frame is sent during the transmission of a message). The overload frame consists of two fields: an overload flag followed by an overload delimiter. The overload flags generated by other nodes (and, as for an active error flag, giving a maximum of twelve dominant bits). The overload delimiter consists of eight recessive bits. An overload frame can be generated by a node as a result of two conditions:

- The node detects a dominant bit during the interframe space, an illegal condition. Exception: The dominant bit is detected during the third bit of IFS. In this case, the receivers will interpret this as a SOF.

- Due to internal conditions, the node is not yet able to begin reception of the next message. A node may generate a maximum of two sequential overload frames to delay the start of the next message.

**Note:** Case 2 should never occur with the MCP2515 due to very short internal delays.

### 2.6 Interframe Space

The interframe space separates a preceding frame (of any type) from a subsequent data or remote frame. The interframe space is composed of at least three recessive bits called the Intermission. This allows nodes time for internal processing before the start of the next message frame. After the intermission, the bus line remains in the recessive state (bus idle) until the next transmission starts.

FIGURE 2-2: **EXTENDED DATA FRAME** End-of-Frame PCK D6I CKC D6I CKC D6I — 16—— CRC Field - 15 — CRC Data Frame (number of bits = 64 + 8N)-Stored in Transmit/Receive Buffers -8N (0 ≤ N ≤ 8)− Data Field -6-Control | Field Data Length Code DCC0 Bit-stuffing DFC3

O BB0

O BLB

EIDO Reserved bits Extended Identifier 8 Stored in Buffers-Arbitration Field EID17 - SRR - ID0 Message Filtering ID3 Identifier-O Start-Of-Frame ID10 ▲

FIGURE 2-4: **ACTIVE ERROR FRAME** Inter-Frame Space or Overload Frame Error Delimiter Error Frame Echo Error Flag 0 0 0 0 0 0 0 Error Flag Data Frame or Remote Frame - 8N (0≤N≤8) Data Field Interrupted Data Frame Bit-stuffing DFC0 Data Length Code Control Field DFC3

o BB0

O IDE Reserved Bit PTR BTR Arbitration Field ID3 Message Filtering Identifier 01 al Start-Of-Frame

## MCP2515

NOTES:

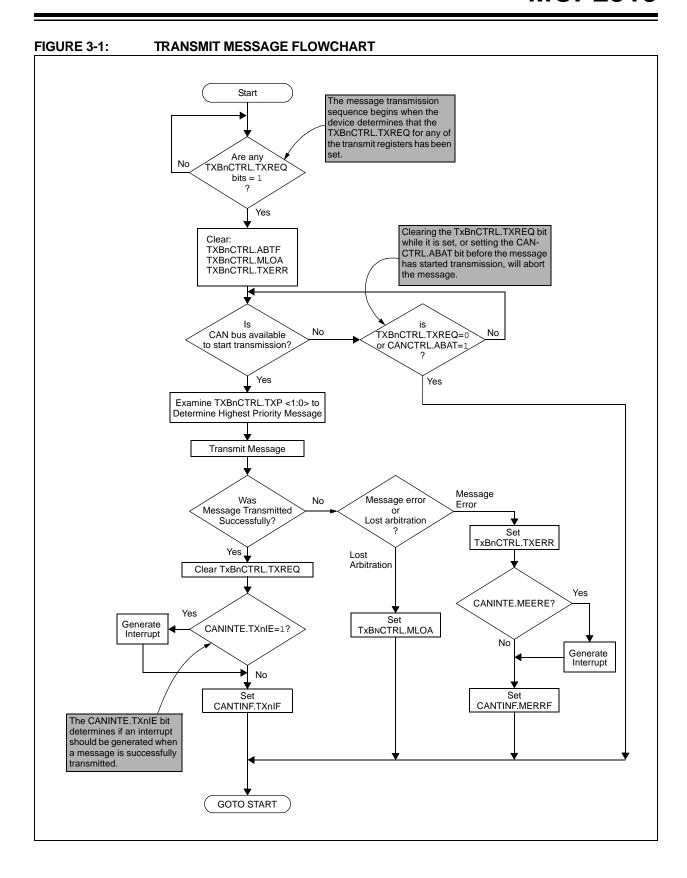

### 3.0 MESSAGE TRANSMISSION

#### 3.1 Transmit Buffers

The MCP2515 implements three transmit buffers. Each of these buffers occupies 14 bytes of SRAM and are mapped into the device memory map.

The first byte, TXBnCTRL, is a control register associated with the message buffer. The information in this register determines the conditions under which the message will be transmitted and indicates the status of the message transmission (see Register 3-2).

Five bytes are used to hold the standard and extended identifiers, as well as other message arbitration information (see Register 3-4 through Register 3-7). The last eight bytes are for the eight possible data bytes of the message to be transmitted (see Register 3-8).

At a minimum, the TXBnSIDH, TXBnSIDL and TXBnDLC registers must be loaded. If data bytes are present in the message, the TXBnDm registers must also be loaded. If the message is to use extended identifiers, the TXBnEIDm registers must also be loaded and the TXBnSIDL.EXIDE bit set.

Prior to sending the message, the MCU must initialize the CANINTE.TXInE bit to enable or disable the generation of an interrupt when the message is sent.

Note: Th

The TXBnCTRL.TXREQ bit must be clear (indicating the transmit buffer is not pending transmission) before writing to the transmit buffer.

### 3.2 Transmit Priority

Transmit priority is a prioritization within the MCP2515 of the pending transmittable messages. This is independent from, and not necessarily related to, any prioritization implicit in the message arbitration scheme built into the CAN protocol.

Prior to sending the SOF, the priority of all buffers that are queued for transmission is compared. The transmit buffer with the highest priority will be sent first. For example, if transmit buffer 0 has a higher priority setting than transmit buffer 1, buffer 0 will be sent first.

If two buffers have the same priority setting, the buffer with the highest buffer number will be sent first. For example, if transmit buffer 1 has the same priority setting as transmit buffer 0, buffer 1 will be sent first.

There are four levels of transmit priority. If TXBnCTRL.TXP<1:0> for a particular message buffer is set to 11, that buffer has the highest possible priority. If TXBnCTRL.TXP<1:0> for a particular message buffer is 00, that buffer has the lowest possible priority.

### 3.3 Initiating Transmission

In order to initiate message transmission, the TXBnCTRL.TXREQ bit must be set for each buffer to be transmitted. This can be accomplished by:

- · Writing to the register via the SPI write command

- · Sending the SPI RTS command

- Setting the TXnRTS pin low for the particular transmit buffer(s) that are to be transmitted

If transmission is initiated via the SPI interface, the TXREQ bit can be set at the same time as the TXP priority bits.

When TXBnCTRL.TXREQ is set, the TXBnCTRL.ABTF, TXBnCTRL.MLOA and TXBnCTRL.TXERR bits will be cleared automatically.

Note:

Setting the TXBnCTRL.TXREQ bit does not initiate a message transmission. It merely flags a message buffer as being ready for transmission. Transmission will start when the device detects that the bus is available.

Once the transmission has completed successfully, the TXBnCTRL.TXREQ bit will be cleared, the CANINTF.TXnIF bit will be set and an interrupt will be generated if the CANINTE.TXnIE bit is set.

If the message transmission fails, the TXBnCTRL.TXREQ will remain set. This indicates that the message is still pending for transmission and one of the following condition flags will be set:

- If the message started to transmit but encountered an error condition, the TXBnCTRL.TXERR and the CANINTF.MERRF bits will be set and an interrupt will be generated on the INT pin if the CANINTE.MERRE bit is set

- If the message is lost, arbitration at the TXBnCTRL.MLOA bit will be set

Note:

If One-shot mode is enabled (CANCTRL.OSM), the above conditions will still exist. However, the TXREQ bit will be cleared and the message will not attempt transmission a second time.

#### 3.4 One-Shot Mode

One-shot mode ensures that a message will only attempt to transmit one time. Normally, if a CAN message loses arbitration, or is destroyed by an error frame, the message is retransmitted. With One-shot mode enabled, a message will only attempt to transmit one time, regardless of arbitration loss or error frame.

One-shot mode is required to maintain time slots in deterministic systems, such as TTCAN.

#### 3.5 TXnRTS PINS

The TXnRTS pins are input pins that can be configured as:

- Request-to-send inputs, which provides an alternative means of initiating the transmission of a message from any of the transmit buffers

- · Standard digital inputs

Configuration and control of these pins is accomplished using the TXRTSCTRL register (see Register 3-3). The TXRTSCTRL register can only be modified when the MCP2515 is in Configuration mode (see **Section 10.0** "**Modes of Operation**"). If configured to operate as a request-to-send pin, the pin is mapped into the respective TXBnCTRL.TXREQ bit for the transmit buffer. The TXREQ bit is latched by the falling edge of the TXnRTS pin. The TXnRTS pins are designed to allow them to be tied directly to the RXnBF pins to automatically initiate a message transmission when the RXnBF pin goes low.

The  $\overline{\text{TXnRTS}}$  pins have internal pull-up resistors of 100 k $\Omega$  (nominal).

### 3.6 Aborting Transmission

The MCU can request to abort a message in a specific message buffer by clearing the associated TXBnCTRL.TXREQ bit.

In addition, all pending messages can be requested to be aborted by setting the CANCTRL.ABAT bit. This bit MUST be reset (typically after the TXREQ bits have been verified to be cleared) to continue transmitting messages. The CANCTRL.ABTF flag will only be set if the abort was requested via the CANCTRL.ABAT bit. Aborting a message by resetting the TXREQ bit does NOT cause the ABTF bit to be set.

Note:

Messages that were transmitting when the abort was requested will continue to transmit. If the message does not successfully complete transmission (i.e., lost arbitration or was interrupted by an error frame), it will then be aborted.

## REGISTER 3-1: TXBnCTRL – TRANSMIT BUFFER n CONTROL REGISTER (ADDRESS: 30h, 40h, 50h)

| U-0   | R-0  | R-0  | R-0   | R/W-0 | U-0 | R/W-0 | R/W-0 |

|-------|------|------|-------|-------|-----|-------|-------|

| _     | ABTF | MLOA | TXERR | TXREQ | _   | TXP1  | TXP0  |

| bit 7 |      |      |       |       |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **Unimplemented:** Read as '0'

bit 6 ABTF: Message Aborted Flag bit

1 = Message was aborted

0 = Message completed transmission successfully

bit 5 MLOA: Message Lost Arbitration bit

1 = Message lost arbitration while being sent

0 = Message did not lose arbitration while being sent

bit 4 TXERR: Transmission Error Detected bit

1 = A bus error occurred while the message was being transmitted

0 = No bus error occurred while the message was being transmitted

bit 3 TXREQ: Message Transmit Request bit

1 = Buffer is currently pending transmission

(MCU sets this bit to request message be transmitted - bit is automatically cleared when

the message is sent)

0 = Buffer is not currently pending transmission

(MCU can clear this bit to request a message abort)

bit 2 Unimplemented: Read as '0'

bit 1-0 **TXP**: Transmit Buffer Priority <1:0> bits

11 = Highest Message Priority

10 = High Intermediate Message Priority

01 = Low Intermediate Message Priority

00 = Lowest Message Priority

## REGISTER 3-2: TXRTSCTRL – TXnRTS PIN CONTROL AND STATUS REGISTER (ADDRESS: 0Dh)

| U-0   | U-0 | R-x   | R-x   | R-x   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|-------|--------|--------|--------|

| _     | _   | B2RTS | B1RTS | B0RTS | B2RTSM | B1RTSM | B0RTSM |

| bit 7 |     |       |       |       |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 Unimplemented: Read as '0'

bit 6 Unimplemented: Read as '0'

bit 5 B2RTS: TX2RTS Pin State bit

Reads state of TX2RTS pin when in Digital Input mode

Reads as '0' when pin is in 'Request-to-Send' mode

bit 4 B1RTS: TX1RTX Pin State bit

- Reads state of TX1RTS pin when in Digital Input mode - Reads as '0' when pin is in 'Request-to-Send' mode

bit 3 **BORTS**: TXORTS Pin State bit

- Reads state of TXORTS pin when in Digital Input mode - Reads as '0' when pin is in 'Request-to-Send' mode

bit 2 **B2RTSM**: TX2RTS Pin mode bit

1 = Pin is used to request message transmission of TXB2 buffer (on falling edge)

0 = Digital input

bit 1 B1RTSM: TX1RTS Pin mode bit

1 = Pin is used to request message transmission of TXB1 buffer (on falling edge)

0 = Digital input

bit 0 **BORTSM**: TXORTS Pin mode bit

1 = Pin is used to request message transmission of TXB0 buffer (on falling edge)

0 = Digital input

## REGISTER 3-3: TXBnSIDH – TRANSMIT BUFFER n STANDARD IDENTIFIER HIGH (ADDRESS: 31h, 41h, 51h)

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 SID: Standard Identifier bits <10:3>

## REGISTER 3-4: TXBnSIDL – TRANSMIT BUFFER n STANDARD IDENTIFIER LOW (ADDRESS: 32h, 42h, 52h)

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID2  | SID1  | SID0  | _     | EXIDE | _     | EID17 | EID16 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-5 **SID**: Standard Identifier bits <2:0> bit 4 **Unimplemented**: Reads as '0'

bit 3 **EXIDE**: Extended Identifier Enable bit

1 = Message will transmit extended identifier0 = Message will transmit standard identifier

bit 2 **Unimplemented**: Reads as '0' bit 1-0 **EID**: Extended Identifier bits <17:16>

## REGISTER 3-5: TXBnEID8 – TRANSMIT BUFFER n EXTENDED IDENTIFIER HIGH (ADDRESS: 33h, 43h, 53h)

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **EID**: Extended Identifier bits <15:8>

## REGISTER 3-6: TXBnEID0 – TRANSMIT BUFFER n EXTENDED IDENTIFIER LOW (ADDRESS: 34h, 44h, 54h)

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **EID**: Extended Identifier bits <7:0>

## REGISTER 3-7: TXBnDLC - TRANSMIT BUFFER n DATA LENGTH CODE (ADDRESS: 35h, 45h, 55h)

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| _     | RTR   | _     | _     | DLC3  | DLC2  | DLC1  | DLC0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **Unimplemented**: Reads as '0'

bit 6 RTR: Remote Transmission Request bit

1 = Transmitted Message will be a Remote Transmit Request

0 = Transmitted Message will be a Data Frame

bit 5-4 **Unimplemented**: Reads as '0'

bit 3-0 **DLC**: Data Length Code <3:0> bits

Sets the number of data bytes to be transmitted (0 to 8 bytes)

Note: It is possible to set the DLC to a value greater than 8, however only 8 bytes are transmitted

## REGISTER 3-8: TXBnDm – TRANSMIT BUFFER n DATA BYTE m (ADDRESS: 36h - 3Dh, 46h - 4Dh, 56h - 5Dh)

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TXBnDm7 | TXBnDm6 | TXBnDm5 | TXBnDm4 | TXBnDm3 | TXBnDm2 | TXBnDm1 | TXBnDm0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **TXBnDm7:TXBnDm0**: Transmit Buffer n Data Field Bytes m

## MCP2515

**NOTES:**

### 4.0 MESSAGE RECEPTION

### 4.1 Receive Message Buffering

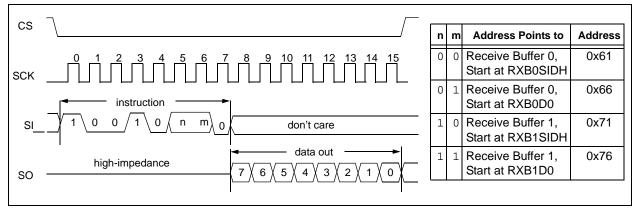

The MCP2515 includes two full receive buffers with multiple acceptance filters for each. There is also a separate Message Assembly Buffer (MAB) that acts as a third receive buffer (see Figure 4-2).

### 4.1.1 MESSAGE ASSEMBLY BUFFER

Of the three receive buffers, the MAB is always committed to receiving the next message from the bus. The MAB assembles all messages received. These messages will be transferred to the RXBn buffers (See Register 4-4 to Register 4-9) only if the acceptance filter criteria is met.

#### 4.1.2 RXB0 AND RXB1

The remaining two receive buffers, called RXB0 and RXB1, can receive a complete message from the protocol engine via the MAB. The MCU can access one buffer, while the other buffer is available for message reception, or for holding a previously received message.

Note:

The entire contents of the MAB is moved into the receive buffer once a message is accepted. This means that, regardless of the type of identifier (standard or extended) and the number of data bytes received, the entire receive buffer is overwritten with the MAB contents. Therefore, the contents of all registers in the buffer must be assumed to have been modified when any message is received.

### 4.1.3 RECEIVE FLAGS/INTERRUPTS

When a message is moved into either of the receive buffers, the appropriate CANINTF.RXnIF bit is set. This bit must be cleared by the MCU in order to allow a new message to be received into the buffer. This bit provides a positive lockout to ensure that the MCU has finished with the message before the MCP2515 attempts to load a new message into the receive buffer.

If the CANINTE.RXnIE bit is set, an interrupt will be generated on the INT pin to indicate that a valid message has been received. In addition, the associated RXnBF pin will drive low if configured as a receive buffer full pin. See **Section 4.4** "**RX0BF and RX1BF Pins**" for details.

### 4.2 Receive Priority

RXB0, the higher priority buffer, has one mask and two message acceptance filters associated with it. The received message is applied to the mask and filters for RXB0 first.

RXB1 is the lower priority buffer, with one mask and four acceptance filters associated with it.

In addition to the message being applied to the RB0 mask and filters first, the lower number of acceptance filters makes the match on RXB0 more restrictive and implies a higher priority for that buffer.

When a message is received, bits <3:0> of the RXBnCTRL register will indicate the acceptance filter number that enabled reception and whether the received message is a remote transfer request.

#### 4.2.1 ROLLOVER

Additionally, the RXB0CTRL register can be configured such that, if RXB0 contains a valid message and another valid message is received, an overflow error will not occur and the new message will be moved into RXB1, regardless of the acceptance criteria of RXB1.

#### 4.2.2 RXM BITS

The RXBnCTRL.RXM bits set special receive modes. Normally, these bits are cleared to 00 to enable reception of all valid messages as determined by the appropriate acceptance filters. In this case, the determination of whether or not to receive standard or extended messages is determined by the RFXnSIDL.EXIDE bit in the acceptance filter register.

If the RXBnCTRL.RXM bits are set to 01 or 10, the receiver will only accept messages with standard or extended identifiers, respectively. If an acceptance filter has the RFXnSIDL.EXIDE bit set such that it does not correspond with the RXBnCTRL.RXM mode, that acceptance filter is rendered useless. These two modes of RXBnCTRL.RXM bits can be used in systems where it is known that only standard or extended messages will be on the bus.

If the RXBnCTRL.RXM bits are set to 11, the buffer will receive all messages, regardless of the values of the acceptance filters. Also, if a message has an error before the EOF, that portion of the message assembled in the MAB before the error frame will be loaded into the buffer. This mode has some value in debugging a CAN system and would not be used in an actual system environment.

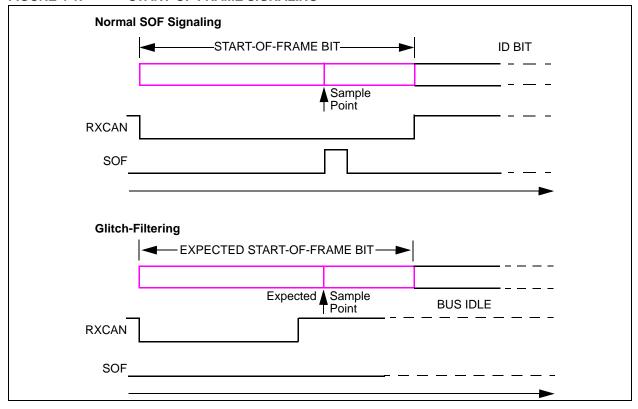

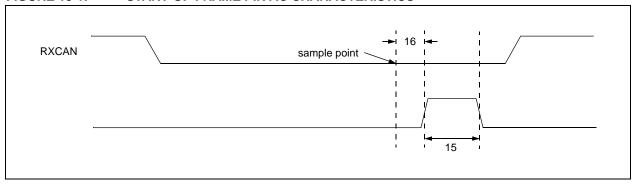

### 4.3 Start-of-Frame Signal

If enabled, the Start-Of-Frame signal is generated on the SOF pin at the beginning of each CAN message detected on the RXCAN pin.

The RXCAN pin monitors an idle bus for a recessive-to-dominant edge. If the dominant condition remains until the sample point, the DSTEMP interprets this as a SOF and a SOF pulse is generated. If the dominant condition does not remain until the sample point, the DSTEMP interprets this as a glitch on the bus and no SOF signal is generated. Figure 4-1 illustrates SOF signalling and glitch-filtering.

As with One-shot mode, one use for SOF signaling is for TTCAN-type systems. In addition, by monitoring both the RXCAN pin and the SOF pin, a MCU can detect early physical bus problems by detecting small glitches before they affect the CAN communications.

### 4.4 RX0BF and RX1BF Pins

In addition to the INT pin, which provides an interrupt signal to the MCU for many different conditions, the receive buffer full pins (RX0BF and RX1BF) can be used to indicate that a valid message has been loaded into RXB0 or RXB1, respectively. The pins have three different configurations (Register 4-1):

- 1. Disabled.

- 2. Buffer Full Interrupt.

- 3. Digital Output.

#### 4.4.1 DISABLED

The RXBnBF pins can be disabled to the high-impedance state by clearing BFPCTRL.BnBFE.

### 4.4.2 CONFIGURED AS BUFFER FULL

The RXBnBF pins can be configured to act as either buffer full interrupt pins or as standard digital outputs. Configuration and status of these pins is available via the BFPCTRL register (Register 4-3). When set to operate in Interrupt mode (by setting BFPCTRL.BxBFE and BFPCTRL.BxBFM bits), these pins are active-low and are mapped to the CANINTF.RXnIF bit for each receive buffer. When this bit goes high for one of the receive buffers (indicating that a valid message has been loaded into the buffer), the corresponding RXBnBF pin will go low. When the CANINTF.RXnIF bit is cleared by the MCU, the corresponding interrupt pin will go to the logic-high state until the next message is loaded into the receive buffer.

FIGURE 4-1: START-OF-FRAME SIGNALING

### 4.4.3 CONFIGURED AS DIGITAL OUTPUT

When used as digital outputs, the BFPCTRL.BxBFM bit must be cleared and BFPCTRL.BnBFE must be set for the associated buffer. In this mode, the state of the pin is controlled by the BFPCTRL.BnBFS bits. Writing a '1' to the BnBFS bit will cause a high level to be driven on the associated buffer full pin, while a '0' will cause the pin to drive low. When using the pins in this mode, the state of the pin should be modified only by using the Bit Modify SPI command to prevent glitches from occurring on either of the buffer full pins.

TABLE 4-1: CONFIGURING RXNBF PINS

| BnBFE | BnBFM | BnBFS | Pin Status               |

|-------|-------|-------|--------------------------|

| 0     | Х     | Х     | Disabled, high-impedance |

| 1     | 1     | Х     | Receive buffer interrupt |

| 1     | 0     | 0     | Digital output = 0       |

| 1     | 0     | 1     | Digital output = 1       |

FIGURE 4-2: RECEIVE BUFFER BLOCK DIAGRAM

RECEIVE FLOW FLOWCHART **FIGURE 4-3:** Start Detect No Start of Message? Yes Begin Loading Message into Message Assembly Buffer (MAB) Valid Generate Error Frame No Message Received? Yes Meets Yes No Yes a filter criteria a filter criteria for RXB0? for RXB1? No Go to Start Determines if the receive register is empty and able to accept a new message Determines if RXB0 can roll over into RXB1, if it is full. Is CANINTF.RX0IF = 0? No Yes RXB0CTRL.BUKT = No Yes Generate Overflow Error Set EFLG.RX0OVR No Move message into RXB0 Generate Overflow Error: CANINTF.RX1IF = 0? Set EFLG.RX10VR Set CANINTF.RX0IF = 1 Move message into RXB1 No Set RXB0CTRL.FILHIT <0> CANINTE.ERRIE = 1? according to which filter criteria Set CANINTF.RX1IF = 1 Set RXB0CTRL.FILHIT <2:0> Generate according to which filter criteria Go to Start Interrupt on INT was met Generate CANINTE.RX0IE = 1 CANINTE.RX1IE = 1 Interrupt on INT Set CANSTAT <3:0> accord-RXB0 RXB1 ₩No ing to which receive buffer the message was loaded into BFPCTRL.B1BFM = 1 Yes BFPCTRL.B0BFM = 1 Yes Set RXBF1 Set RXBF0 and and Pin = 0Pin = 0BF1CTRL.B1BFE = 1? BF1CTRL.B0BFE = 1 No No

REGISTER 4-1: RXB0CTRL - RECEIVE BUFFER 0 CONTROL (ADDRESS: 60h)

| U-0   | R/W-0 | R/W-0 | U-0 | R-0   | R/W-0 | R-0   | R-0     |

|-------|-------|-------|-----|-------|-------|-------|---------|

| _     | RXM1  | RXM0  | _   | RXRTR | BUKT  | BUKT1 | FILHIT0 |

| bit 7 |       |       |     |       |       |       | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **Unimplemented:** Read as '0'

bit 6-5 **RXM**: Receive Buffer Operating Mode bits

11 = Turn mask/filters off; receive any message

10 = Receive only valid messages with extended identifiers that meet filter criteria 01 = Receive only valid messages with standard identifiers that meet filter criteria

00 = Receive all valid messages using either standard or extended identifiers that meet filter criteria

bit 4 Unimplemented: Read as '0'

bit 3 RXRTR: Received Remote Transfer Request bit

1 = Remote Transfer Request Received

0 = No Remote Transfer Request Received

bit 2 **BUKT**: Rollover Enable bit

1 = RXB0 message will rollover and be written to RXB1 if RXB0 is full

0 = Rollover disabled

bit 1 **BUKT1**: Read-only Copy of BUKT bit (used internally by the MCP2515)

bit 0 FILHIT: Filter Hit bit - indicates which acceptance filter enabled reception of message

1 = Acceptance Filter 1 (RXF1)

0 = Acceptance Filter 0 (RXF0)

Note: If a rollover from RXB0 to RXB1 occurs, the FILHIT bit will reflect the filter that accepted

the message that rolled over.

REGISTER 4-2: RXB1CTRL – RECEIVE BUFFER 1 CONTROL (ADDRESS: 70h)

| U-0   | R/W-0 | R/W-0 | U-0 | R-0   | R-0     | R-0     | R-0     |

|-------|-------|-------|-----|-------|---------|---------|---------|

| _     | RXM1  | RXM0  | _   | RXRTR | FILHIT2 | FILHIT1 | FILHIT0 |

| bit 7 |       |       |     |       |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 Unimplemented: Read as '0'

bit 6-5 **RXM**: Receive Buffer Operating Mode bits

11 = Turn mask/filters off; receive any message

10 = Receive only valid messages with extended identifiers that meet filter criteria

01 = Receive only valid messages with standard identifiers that meet filter criteria

00 = Receive all valid messages using either standard or extended identifiers that meet filter criteria

bit 4 Unimplemented: Read as '0'

bit 3 RXRTR: Received Remote Transfer Request bit

1 = Remote Transfer Request Received

0 = No Remote Transfer Request Received

bit 2-0 FILHIT: Filter Hit bits - indicates which acceptance filter enabled reception of message

101 = Acceptance Filter 5 (RXF5)

100 = Acceptance Filter 4 (RXF4)

011 = Acceptance Filter 3 (RXF3)

010 = Acceptance Filter 2 (RXF2)

001 = Acceptance Filter 1 (RXF1) (Only if BUKT bit set in RXB0CTRL)

000 = Acceptance Filter 0 (RXF0) (Only if BUKT bit set in RXB0CTRL)

## REGISTER 4-3: BFPCTRL – RXnBF PIN CONTROL AND STATUS (ADDRESS: 0Ch)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | B1BFS | B0BFS | B1BFE | B0BFE | B1BFM | B0BFM |

| bit 7 |     |       |       |       |       |       | bit 0 |

Legend:

bit 4

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 Unimplemented: Read as '0'

bit 6 Unimplemented: Read as '0'

bit 5 B1BFS: RX1BF Pin State bit (Digital Output mode only)

- Reads as '0' when RX1BF is configured as interrupt pin

BOBFS: RXOBF Pin State bit (Digital Output mode only)

- Reads as '0' when RX0BF is configured as interrupt pin bit 3 **B1BFE**: RX1BF Pin Function Enable bit

1 = Pin function enabled, operation mode determined by B1BFM bit

0 = Pin function disabled, pin goes to high-impedance state

bit 2 **B0BFE**: RX0BF Pin Function Enable bit

1 = Pin function enabled, operation mode determined by B0BFM bit

0 = Pin function disabled, pin goes to high-impedance state

bit 1 **B1BFM**: RX1BF Pin Operation Mode bit

1 = Pin is used as interrupt when valid message loaded into RXB1

0 = Digital Output mode

bit 0 **B0BFM**: RX0BF Pin Operation Mode bit

1 = Pin is used as interrupt when valid message loaded into RXB0

0 = Digital Output mode

## REGISTER 4-4: RXBnSIDH – RECEIVE BUFFER n STANDARD IDENTIFIER HIGH (ADDRESS: 61h, 71h)

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| SID10 | SID9 | SID8 | SID7 | SID6 | SID5 | SID4 | SID3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **SID**: Standard Identifier bits <10:3>

These bits contain the eight most significant bits of the Standard Identifier for the received message

## REGISTER 4-5: RXBnSIDL – RECEIVE BUFFER n STANDARD IDENTIFIER LOW (ADDRESS: 62h, 72h)

| R-x   | R-x  | R-x  | R-x | R-x | U-0 | R-x   | R-x   |

|-------|------|------|-----|-----|-----|-------|-------|

| SID2  | SID1 | SID0 | SRR | IDE | _   | EID17 | EID16 |

| bit 7 |      |      | _   |     | _   |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-5 SID: Standard Identifier bits <2:0>

These bits contain the three least significant bits of the Standard Identifier for the received message

bit 4 SRR: Standard Frame Remote Transmit Request bit (valid only if IDE bit = '0')

1 = Standard Frame Remote Transmit Request Received

0 = Standard Data Frame Received

bit 3 IDE: Extended Identifier Flag bit

This bit indicates whether the received message was a Standard or an Extended Frame

1 = Received message was an Extended Frame0 = Received message was a Standard Frame

bit 2 **Unimplemented:** Reads as '0'

bit 1-0 **EID**: Extended Identifier bits <17:16>

These bits contain the two most significant bits of the Extended Identifier for the received message

## REGISTER 4-6: RXBnEID8 – RECEIVE BUFFER n EXTENDED IDENTIFIER HIGH (ADDRESS: 63h, 73h)

| R-x   | R-x   | R-x   | R-x   | R-x   | R-x   | R-x  | R-x   |

|-------|-------|-------|-------|-------|-------|------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9 | EID8  |

| bit 7 |       |       |       |       |       |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **EID**: Extended Identifier bits <15:8>

These bits hold bits 15 through 8 of the Extended Identifier for the received message

## REGISTER 4-7: RXBnEID0 – RECEIVE BUFFER n EXTENDED IDENTIFIER LOW (ADDRESS: 64h, 74h)

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| EID7  | EID6 | EID5 | EID4 | EID3 | EID2 | EID1 | EID0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **EID**: Extended Identifier bits <7:0>

These bits hold the least significant eight bits of the Extended Identifier for the received message

## REGISTER 4-8: RXBnDLC – RECEIVE BUFFER n DATA LENGHT CODE (ADDRESS: 65h, 75h)

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| EID7  | EID6 | EID5 | EID4 | EID3 | EID2 | EID1 | EID0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 Unimplemented: Reads as '0'

bit 6 RTR: Extended Frame Remote Transmission Request bit

(valid only when RXBnSIDL.IDE = '1')

1 = Extended Frame Remote Transmit Request Received

0 = Extended Data Frame Received

bit 5 **RB1:** Reserved Bit 1 bit 4 **RB0:** Reserved Bit 0

bit 3-0 **DLC**: Data Length Code bits <3:0>

Indicates number of data bytes that were received

## REGISTER 4-9: RXBnDM – RECEIVE BUFFER n DATA BYTE M (ADDRESS: 66h - 6Dh, 76h - 7Dh)

| R-x    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RBnDm7 | RBnDm6 | RBnDm5 | RBnDm4 | RBnDm3 | RBnDm2 | RBnDm1 | RBnDm0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

$R = Readable \ bit \ W = Writable \ bit \ U = Unimplemented \ bit, read as '0'$

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 7-0 RBnDm7:RBnDm0: Receive Buffer n Data Field Bytes m

Eight bytes containing the data bytes for the received message

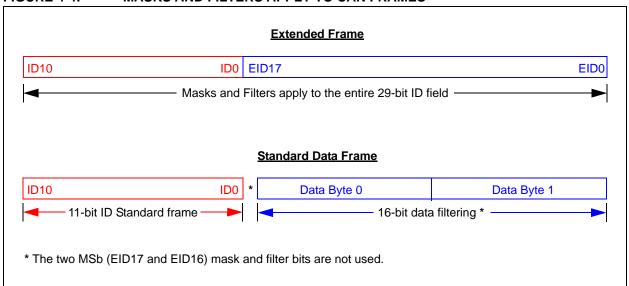

## 4.5 Message Acceptance Filters and Masks

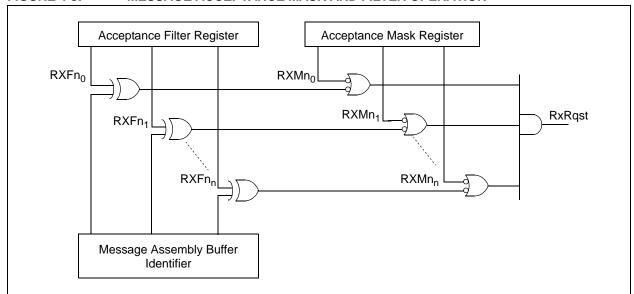

The message acceptance filters and masks are used to determine if a message in the message assembly buffer should be loaded into either of the receive buffers (see Figure 4-5). Once a valid message has been received into the MAB, the identifier fields of the message are compared to the filter values. If there is a match, that message will be loaded into the appropriate receive buffer.

### 4.5.1 DATA BYTE FILTERING

When receiving standard data frames (11-bit identifier), the DSTEMP automatically applies 16 bits of masks and filters normally associated with extended identifiers to the first 16 bits of the data field (data bytes 0 and 1). Figure 4-4 illustrates how masks and filters apply to extended and standard data frames.

Data byte filtering reduces the load on the MCU when implementing Higher Layer Protocols (HLPs) that filter on the first data byte (e.g., DeviceNet<sup>™</sup>).

#### 4.5.2 FILTER MATCHING

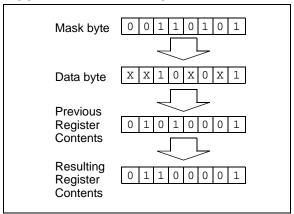

The filter masks (see Register 4-14 through Register 4-17) are used to determine which bits in the identifier are examined with the filters. A truth table is shown in Table 4-2 that indicates how each bit in the

identifier is compared to the masks and filters to determine if the message should be loaded into a receive buffer. The mask essentially determines which bits to apply the acceptance filters to. If any mask bit is set to a zero, that bit will automatically be accepted, regardless of the filter bit.

TABLE 4-2: FILTER/MASK TRUTH TABLE

| Mask Bit<br>n | Filter Bit n | Message<br>Identifier<br>bit | Accept or<br>Reject bit<br>n |

|---------------|--------------|------------------------------|------------------------------|

| 0             | Х            | Х                            | Accept                       |

| 1             | 0            | 0                            | Accept                       |

| 1             | 0            | 1                            | Reject                       |

| 1             | 1            | 0                            | Reject                       |

| 1             | 1            | 1                            | Accept                       |

**Note:** X = don't care

As shown in the receive buffers block diagram (Figure 4-2), acceptance filters RXF0 and RXF1 (and filter mask RXM0) are associated with RXB0. Filters RXF2, RXF3, RXF4, RXF5 and mask RXM1 are associated with RXB1.

FIGURE 4-4: MASKS AND FILTERS APPLY TO CAN FRAMES

### 4.5.3 FILHIT BITS

Filter matches on received messages can be determined by the FILHIT bits in the associated RXBnCTRL register. RXB0CTRL.FILHIT0 for buffer 0 and RXB1CTRL.FILHIT<2:0> for buffer 1.

The three FILHIT bits for receive buffer 1 (RXB1) are coded as follows:

- 101 = Acceptance Filter 5 (RXF5)

- 100 = Acceptance Filter 4 (RXF4)

- 011 = Acceptance Filter 3 (RXF3)

- 010 = Acceptance Filter 2 (RXF2)

- 001 = Acceptance Filter 1 (RXF1)

- 000 = Acceptance Filter 0 (RXF0)

Note: 000 and 001 can only occur if the BUKT bit in RXB0CTRL is set, allowing RXB0 messages to roll over into RXB1.

RXB0CTRL contains two copies of the BUKT bit and the FILHIT<0> bit.

The coding of the BUKT bit enables these three bits to be used similarly to the RXB1CTRL.FILHIT bits and to distinguish a hit on filter RXF0 and RXF1 in either RXB0 or after a roll over into RXB1.

- 111 = Acceptance Filter 1 (RXB1)

- 110 = Acceptance Filter 0 (RXB1)

- 001 = Acceptance Filter 1 (RXB0)

- 000 = Acceptance Filter 0 (RXB0)

If the BUKT bit is clear, there are six codes corresponding to the six filters. If the BUKT bit is set, there are six codes corresponding to the six filters, plus two additional codes corresponding to RXF0 and RXF1 filters that roll over into RXB1.

### 4.5.4 MULTIPLE FILTER MATCHES

If more than one acceptance filter matches, the FILHIT bits will encode the binary value of the lowest numbered filter that matched. For example, if filter RXF2 and filter RXF4 match, FILHIT will be loaded with the value for RXF2. This essentially prioritizes the acceptance filters with a lower-numbered filter having higher priority. Messages are compared to filters in ascending order of filter number. This also insures that the message will only be received into one buffer. This implies that RXB0 has a higher priority than RXB1.

## 4.5.5 CONFIGURING THE MASKS AND FILTERS

The mask and filter registers can only be modified when the MCP2515 is in Configuration mode (see **Section 10.0 "Modes of Operation"**).

#### FIGURE 4-5: MESSAGE ACCEPTANCE MASK AND FILTER OPERATION

## REGISTER 4-10: RXFnSIDH – FILTER n STANDARD IDENTIFIER HIGH (ADDRESS: 00h, 04h, 08h, 10h, 14h, 18h)

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 SID: Standard Identifier Filter bits <10:3>

These bits hold the filter bits to be applied to bits <10:3> of the Standard Identifier portion of a received message

## REGISTER 4-11: RXFnSIDL – FILTER n STANDARD IDENTIFIER LOW (ADDRESS: 01h, 05h, 09h, 11h, 15h, 19h)

|   | R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|---|-------|-------|-------|-----|-------|-----|-------|-------|

|   | SID2  | SID1  | SID0  | _   | EXIDE | _   | EID17 | EID16 |

| Ī | bit 7 |       |       |     |       |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-5 SID: Standard Identifier Filter bits <2:0>

These bits hold the filter bits to be applied to bits <2:0> of the Standard Identifier portion of a received

message

bit 4 **Unimplemented**: Reads as '0'

bit 3 **EXIDE**: Extended Identifier Enable bit

1 = Filter is applied only to Extended Frames

0 = Filter is applied only to Standard Frames

bit 2 **Unimplemented**: Reads as '0'

bit 1-0 **EID**: Extended Identifier Filter bits <17:16>

These bits hold the filter bits to be applied to bits <17:16> of the Extended Identifier portion of a

received message

## REGISTER 4-12: RXFnEID8 – FILTER n EXTENDED IDENTIFIER HIGH (ADDRESS: 02h, 06h, 0Ah, 12h, 16h, 1Ah)

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **EID**: Extended Identifier bits <15:8>

These bits hold the filter bits to be applied to bits <15:8> of the Extended Identifier portion of a received message

## REGISTER 4-13: RXFnEID0 – FILTER n EXTENDED IDENTIFIER LOW (ADDRESS: 03h, 07h, 0Bh, 13h, 17h, 1Bh)

|   | R/W-x |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| Ī | bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **EID**: Extended Identifier bits <7:0>

These bits hold the filter bits to be applied to the bits <7:0> of the Extended Identifier portion of a received message

## REGISTER 4-14: RXMnSIDH – MASK n STANDARD IDENTIFIER HIGH (ADDRESS: 20h, 24h)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 SID: Standard Identifier Mask bits <10:3>

These bits hold the mask bits to be applied to bits <10:3> of the Standard Identifier portion of a received message

## REGISTER 4-15: RXMnSIDL – MASK n STANDARD IDENTIFIER LOW (ADDRESS: 21h, 25h)

| R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----|-----|-----|-------|-------|

| SID2  | SID1  | SID0  | _   | _   | _   | EID17 | EID16 |

| bit 7 |       |       |     |     |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-5 SID: Standard Identifier Mask bits <2:0>

These bits hold the mask bits to be applied to bits<2:0> of the Standard Identifier portion of a received message

bit 4-2 **Unimplemented**: Reads as '0'

bit 1-0 **EID**: Extended Identifier Mask bits <17:16>

These bits hold the mask bits to be applied to bits <17:16> of the Extended Identifier portion of a

received message

## REGISTER 4-16: RXMnEID8 – MASK n EXTENDED IDENTIFIER HIGH (ADDRESS: 22h, 26h)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **EID**: Extended Identifier bits <15:8>

These bits hold the filter bits to be applied to bits <15:8> of the Extended Identifier portion of a received

message

## REGISTER 4-17: RXMnEID0 – MASK n EXTENDED IDENTIFIER LOW (ADDRESS: 23h, 27h)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **EID**: Extended Identifier Mask bits <7:0>

These bits hold the mask bits to be applied to the bits <7:0> of the Extended Identifier portion of a received message

### 5.0 BIT TIMING

All nodes on a given CAN bus must have the same nominal bit rate. The CAN protocol uses Non Return to Zero (NRZ) coding, which does not encode a clock within the data stream. Therefore, the receive clock must be recovered by the receiving nodes and synchronized to the transmitter's clock.

As oscillators and transmission times may vary from node to node, the receiver must have some type of Phase Lock Loop (PLL) synchronized to data transmission edges to synchronize and maintain the receiver clock. Since the data is NRZ-coded, it is necessary to include bit-stuffing to insure that an edge occurs at least every six bit times to maintain the Digital Phase Lock Loop (DPLL) synchronization.

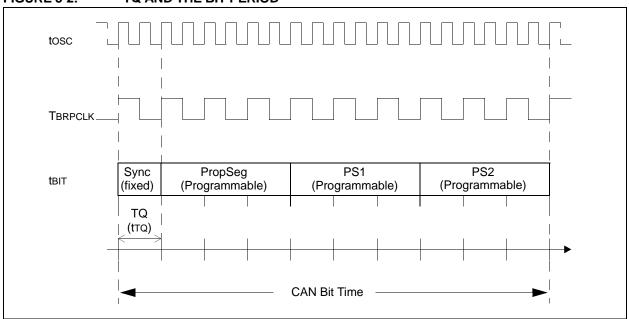

The bit timing of the MCP2515 is implemented using a DPLL that is configured to synchronize to the incoming data, as well as provide the nominal timing for the transmitted data. The DPLL breaks each bit time into multiple segments made up of minimal periods of time, called the Time Quanta (TQ).

Bus timing functions executed within the bit time frame (such as synchronization to the local oscillator, network transmission delay compensation and sample point positioning) are defined by the programmable bit timing logic of the DPLL.

### 5.1 The CAN Bit Time

All devices on the CAN bus must use the same bit rate. However, all devices are not required to have the same master oscillator clock frequency. For the different clock frequencies of the individual devices, the bit rate has to be adjusted by appropriately setting the baud rate prescaler and number of time quanta in each segment.

The CAN bit time is made up of non-overlapping segments. Each of these segments are made up of integer units called Time Quanta (TQ), explained later in this data sheet. The Nominal Bit Rate (NBR) is defined in the CAN specification as the number of bits per second transmitted by an ideal transmitter with no resynchronization. It can be described with the equation:

#### **EQUATION 5-1:**

$$NBR = f_{bit} = \frac{1}{t_{bit}}$$

### **Nominal Bit Time**

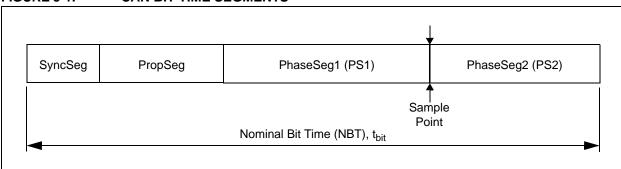

The Nominal Bit Time (NBT) (t<sub>bit</sub>) is made up of nonoverlapping segments (Figure 5-1). Therefore, the NBT is the summation of the following segments:

$$t_{bit} = t_{SyncSeg} + t_{PropSeg} + t_{PS1} + t_{PS2}$$

Associated with the NBT are the sample point, Synchronization Jump Width (SJW) and Information Processing Time (IPT), which are explained later.

### SYNCHRONIZATION SEGMENT

The Synchronization Segment (SyncSeg) is the first segment in the NBT and is used to synchronize the nodes on the bus. Bit edges are expected to occur within the SyncSeg. This segment is fixed at 1 TQ.

FIGURE 5-1: CAN BIT TIME SEGMENTS

### PROPAGATION SEGMENT

The Propagation Segment (PropSeg) exists to compensate for physical delays between nodes. The propagation delay is defined as twice the sum of the signal's propagation time on the bus line, including the delays associated with the bus driver. The PropSeg is programmable from  $1-8\ TQ$ .

# PHASE SEGMENT 1 (PS1) AND PHASE SEGMENT 2 (PS2)

The two phase segments, PS1 and PS2, are used to compensate for edge phase errors on the bus. PS1 can be lengthened (or PS2 shortened) by resyncronization. PS1 is programmable from  $1-8\,\mathrm{TQ}$  and PS2 is programmable from  $2-8\,\mathrm{TQ}$ .

### SAMPLE POINT

The sample point is the point in the bit time at which the logic level is read and interpreted. The sample point is located at the end of PS1. The exception to this rule is if the sample mode is configured to sample three times per bit. In this case, while the bit is still sampled at the end of PS1, two additional samples are taken at one-half TQ intervals prior to the end of PS1, with the value of the bit being determined by a majority decision.

### INFORMATION PROCESSING TIME

The Information Processing Time (IPT) is the time required for the logic to determine the bit level of a sampled bit. The IPT begins at the sample point, is measured in TQ and is fixed at 2 TQ for the Microchip CAN module. Since PS2 also begins at the sample point and is the last segment in the bit time, it is required that the PS2 minimum is not less than the IPT.

Therefore:

$$PS2_{min} = IPT = 2TQ$$

### SYNCHRONIZATION JUMP WIDTH

The Synchronization Jump Width (SJW) adjusts the bit clock as necessary by 1 – 4 TQ (as configured) to maintain synchronization with the transmitted message. Synchronization is covered in more detail later in this data sheet.

### **Time Quantum**

Each of the segments that make up a bit time are made up of integer units called Time Quanta (TQ). The length of each Time Quantum is based on the oscillator period ( $t_{OSC}$ ). The base TQ equals twice the oscillator period. Figure 5-2 shows how the bit period is derived from  $T_{OSC}$  and TQ. The TQ length equals one TQ clock period ( $t_{BRPCLK}$ ), which is programmable using a programmable prescaler, called the Baud Rate Prescaler (BRP). This is illustrated in the following equation:

### **EQUATION 5-2:**

$$TQ = 2 \cdot BRP \cdot T_{OSC} = \frac{2 \cdot BRP}{F_{OSC}}$$

Where: BRP equals the configuration as shown in Register 5-1.

FIGURE 5-2: TQ AND THE BIT PERIOD

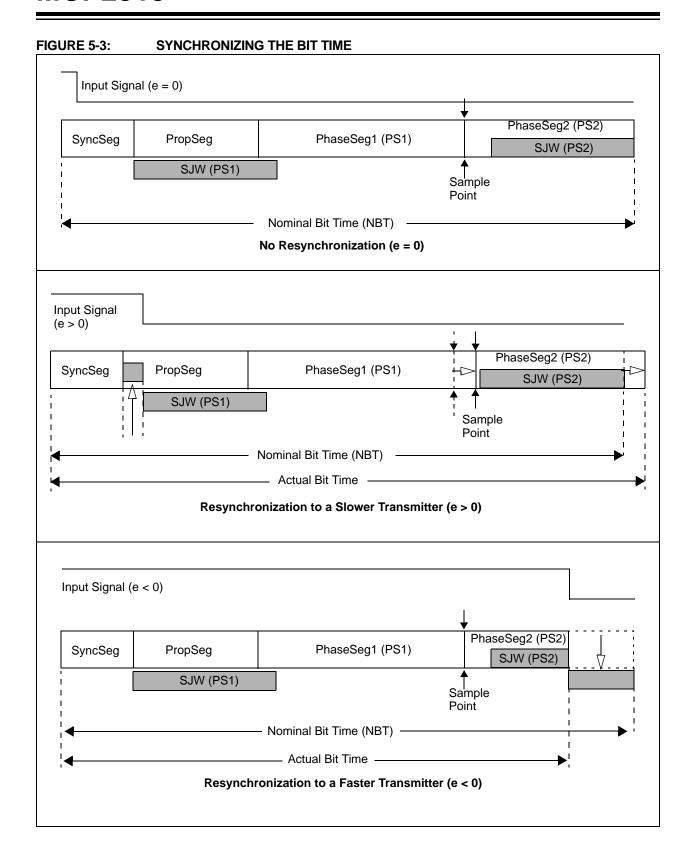

### 5.2 Synchronization

To compensate for phase shifts between the oscillator frequencies of each of the nodes on the bus, each CAN controller must be able to synchronize to the relevant signal edge of the incoming signal. Synchronization is the process by which the DPLL function is implemented.

When an edge in the transmitted data is detected, the logic will compare the location of the edge to the expected time (SyncSeg). The circuit will then adjust the values of PS1 and PS2 as necessary.

There are two mechanisms used for synchronization:

- 1. Hard synchronization.

- 2. Resynchronization.

#### 5.2.1 HARD SYNCHRONIZATION

Hard synchronization is only performed when there is a recessive-to-dominant edge during a BUS IDLE condition, indicating the start of a message. After hard synchronization, the bit time counters are restarted with SyncSeg.

Hard synchronization forces the edge that has occurred to lie within the synchronization segment of the restarted bit time. Due to the rules of synchronization, if a hard synchronization occurs, there will not be a resynchronization within that bit time.

#### 5.2.2 RESYNCHRONIZATION

As a result of resynchronization, PS1 may be lengthened or PS2 may be shortened. The amount of lengthening or shortening of the phase buffer segments has an upper-bound, given by the Synchronization Jump Width (SJW).

The value of the SJW will be added to PS1 or subtracted from PS2 (see Figure 5-3). The SJW represents the loop filtering of the DPLL. The SJW is programmable between 1 TQ and 4 TQ.

### 5.2.2.1 Phase Errors

The NRZ bit coding method does not encode a clock into the message. Clocking information will only be derived from recessive-to-dominant transitions. The property which states that only a fixed maximum number of successive bits have the same value (bit-stuffing) ensures resynchronization to the bit stream during a frame.

The phase error of an edge is given by the position of the edge relative to SyncSeg, measured in TQ. The phase error is defined in magnitude of TQ as follows:

- e = 0 if the edge lies within SYNCSEG.

- e > 0 if the edge lies before the SAMPLE POINT (TQ is added to PS1).

- e < 0 if the edge lies after the SAMPLE POINT of the previous bit (TQ is subtracted from PS2).

### 5.2.2.2 No Phase Error (e = 0)

If the magnitude of the phase error is less than or equal to the programmed value of the SJW, the effect of a resynchronization is the same as that of a hard synchronization.

### 5.2.2.3 Positive Phase Error (e > 0)

If the magnitude of the phase error is larger than the SJW and, if the phase error is positive, PS1 is lengthened by an amount equal to the SJW.

### 5.2.2.4 Negative Phase Error (e < 0)

If the magnitude of the phase error is larger than the resynchronization jump width and the phase error is negative, PS2 is shortened by an amount equal to the SJW.

### 5.2.3 SYNCHRONIZATION RULES

- Only recessive-to-dominant edges will be used for synchronization.

- Only one synchronization within one bit time is allowed.

- An edge will be used for synchronization only if the value detected at the previous sample point (previously read bus value) differs from the bus value immediately after the edge.

- 4. A transmitting node will not resynchronize on a positive phase error (e > 0).

- If the absolute magnitude of the phase error is greater than the SJW, the appropriate phase segment will adjust by an amount equal to the SJW.

### 5.3 Programming Time Segments

Some requirements for programming of the time segments:

- PropSeg + PS1 >= PS2

- PropSeg + PS1 >= TDELAY

- PS2 > SJW

For example, assuming that a 125 kHz CAN baud rate with Fosc = 20 MHz is desired:

Tosc = 50 ns, choose BRP<5:0> = 04h, then TQ = 500 ns. To obtain 125 kHz, the bit time must be 16 TQ.

Typically, the sampling of the bit should take place at about 60-70% of the bit time, depending on the system parameters. Also, typically, the TDELAY is 1-2 TQ.

SyncSeg = 1 TQ and PropSeg = 2 TQ. So setting PS1 = 7 TQ would place the sample at 10 TQ after the transition. This would leave 6 TQ for PS2.

Since PS2 is 6, according to the rules, SJW could be a maximum of 4 Tq. However, a large SJW is typically only necessary when the clock generation of the different nodes is inaccurate or unstable, such as using ceramic resonators. So a SJW of 1 is usually enough.

### 5.4 Oscillator Tolerance

The bit timing requirements allow ceramic resonators to be used in applications with transmission rates of up to 125 kbit/sec as a rule of thumb. For the full bus speed range of the CAN protocol, a quartz oscillator is required. A maximum node-to-node oscillator variation of 1.7% is allowed.

# 5.5 Bit Timing Configuration Registers

The configuration registers (CNF1, CNF2, CNF3) control the bit timing for the CAN bus interface. These registers can only be modified when the MCP2515 is in Configuration mode (see **Section 10.0 "Modes of Operation"**).

### 5.5.1 CNF1

The BRP<5:0> bits control the baud rate prescaler. These bits set the length of TQ relative to the OSC1 input frequency, with the minimum TQ length being 2 Tosc (when BRP<5:0> =  $^{\circ}$ b0000000'). The SJW<1:0> bits select the SJW in terms of number of TQs.

### 5.5.2 CNF2

The PRSEG<2:0> bits set the length (in TQ's) of the propagation segment. The PHSEG1<2:0> bits set the length (in TQ's) of PS1.

The SAM bit controls how many times the RXCAN pin is sampled. Setting this bit to a '1' causes the bus to be sampled three times: twice at To/2 before the sample point and once at the normal sample point (which is at the end of PS1). The value of the bus is determined to be the majority sampled. If the SAM bit is set to a '0', the RXCAN pin is sampled only once at the sample point.

The BTLMODE bit controls how the length of PS2 is determined. If this bit is set to a '1', the length of PS2 is determined by the PHSEG2<2:0> bits of CNF3 (see Section 5.5.3 "CNF3"). If the BTLMODE bit is set to a '0', the length of PS2 is greater than that of PS1 and the information processing time (which is fixed at 2 TQ for the MCP2515).

#### 5.5.3 CNF3

The PHSEG2<2:0> bits set the length (in TQ's) of PS2, if the CNF2.BTLMODE bit is set to a '1'. If the BTLMODE bit is set to a '0', the PHSEG2<2:0> bits have no effect.

### REGISTER 5-1: CNF1 – CONFIGURATION 1 (ADDRESS: 2Ah)

|       | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|       | SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 | 7     |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 SJW: Synchronization Jump Width Length bits <1:0>

11 = Length = 4 x TQ

$10 = \text{Length} = 3 \times \text{TQ}$

01 = Length = 2 x TQ00 = Length = 1 x TQ

bit 5-0 BRP: Baud Rate Prescaler bits <5:0>

$TQ = 2 \times (BRP + 1)/Fosc$

# REGISTER 5-2: CNF2 – CONFIGURATION 1 (ADDRESS: 29h)

| R/W-0   | R/W-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|---------|-------|---------|---------|---------|--------|--------|--------|

| BTLMODE | SAM   | PHSEG12 | PHSEG11 | PHSEG10 | PRSEG2 | PRSEG1 | PRSEG0 |

| bit 7   |       |         |         |         |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 BTLMODE: PS2 Bit Time Length bit

1 = Length of PS2 determined by PHSEG22:PHSEG20 bits of CNF3

0 = Length of PS2 is the greater of PS1 and IPT (2 TQ)

bit 6 SAM: Sample Point Configuration bit

1 = Bus line is sampled three times at the sample point

0 = Bus line is sampled once at the sample point

bit 5-3 PHSEG1: PS1 Length bits<2:0>

(PHSEG1 + 1) x TQ

bit 2-0 PRSEG: Propagation Segment Length bits <2:0>

(PRSEG + 1) x TQ

# REGISTER 5-3: CNF3 - CONFIGURATION 1 (ADDRESS: 28h)

| R/W-0 | R/W-0  | U-0 | U-0 | U-0 | R/W-0   | R/W-0   | R/W-0   |

|-------|--------|-----|-----|-----|---------|---------|---------|

| SOF   | WAKFIL | _   | _   | _   | PHSEG22 | PHSEG21 | PHSEG20 |

| bit 7 |        |     | _   | _   | _       |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 SOF: Start-of-Frame signal bit

If CANCTRL.CLKEN = 1:

1 = CLKOUT pin enabled for SOF signal 0 = CLKOUT pin enabled for clockout function If CANCTRL.CLKEN = 0, Bit is don't care.

bit 6 WAKFIL: Wake-up Filter bit

1 = Wake-up filter enabled0 = Wake-up filter disabled

bit 5-3 **Unimplemented**: Reads as '0' bit 2-0 **PHSEG2**: PS2 Length bits<2:0>

(PHSEG2 + 1) x TQ

Minimum valid setting for PS2 is 2 TQ

**NOTES:**

### 6.0 ERROR DETECTION

The CAN protocol provides sophisticated error detection mechanisms. The following errors can be detected.

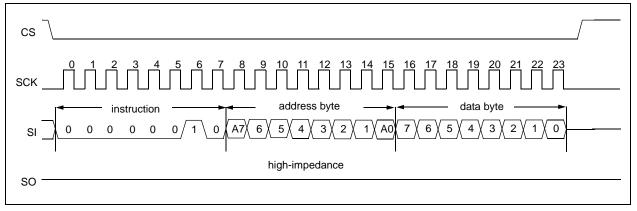

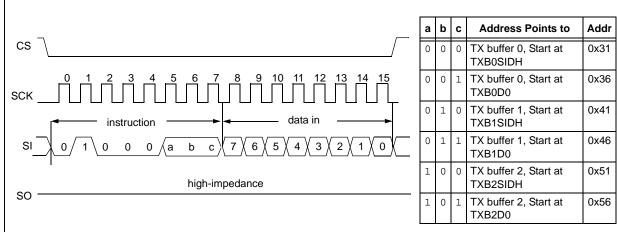

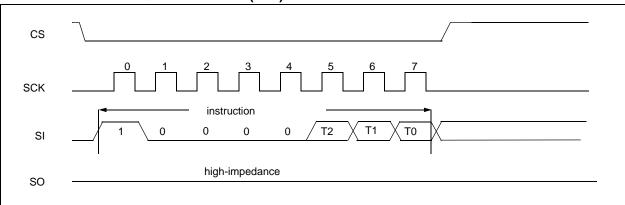

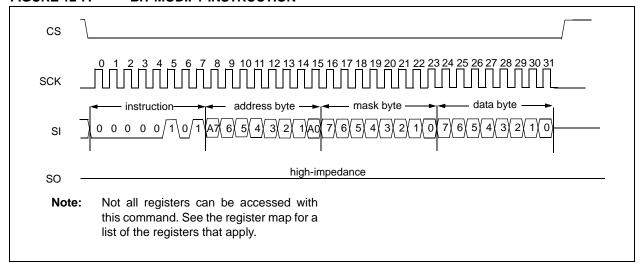

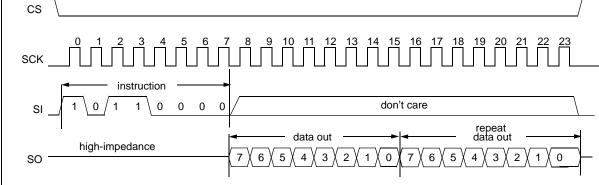

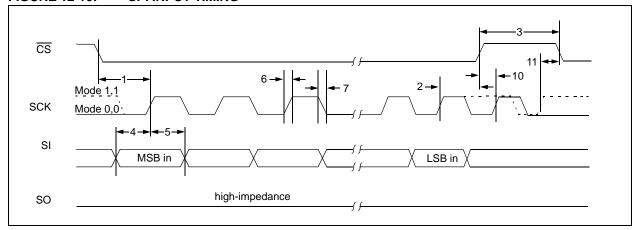

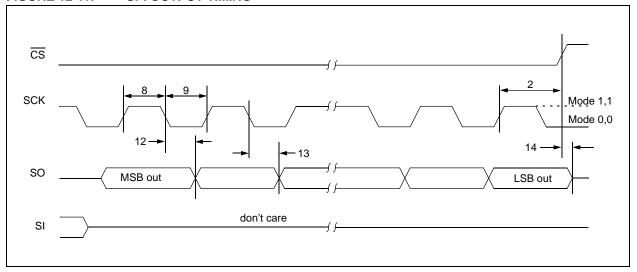

### 6.1 CRC Error